# Design and Analysis of VLSI Subsystems Dr. Madhav Rao Department of Electronics and Communication Engineering International Institute of Information Technology, Bangalore

Lecture - 60 Repeater Design and Energy-Delay-Product

(Refer Slide Time: 00:17)

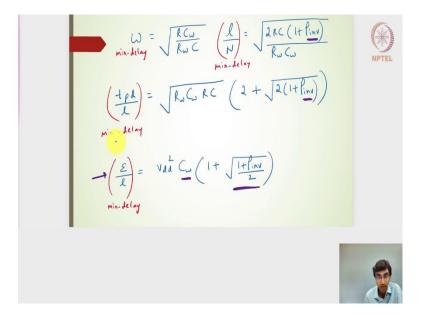

This is what we had derived till the last class. We had an optimum w value, optimum width value, optimum l/N value. This is the optimum l/N value for achieving the minimum delay and that is why I have written in the subscript as the minimum delay for the optimum w and optimum l/N. It is a function of RC and R<sub>w</sub> and C<sub>w</sub>, l/N optimum l/N is a function of RC R<sub>w</sub> C<sub>w</sub> and of course it depends also on the normalized parasitic factor. If it is a folded design technology, then in that case it will be 0.5 otherwise it will be a conventional design technology will give me 1.

If I use this particular optimum parameters and what should be the delay per unit length, the propagation delay per unit length for the wire with repeaters will be given in the form of this particular expression. Again, it is a function of  $R_w C_w RC$  and then the normalized parasitic factor.

Energy per unit length it considers all the capacitance that are there for the N segments of the wire with the repeaters. So, this includes the wire capacitance as well as it includes the parasitic capacitance and then whatever the input gate capacitance. Using this particular optimized parameter of w and l/N, we have arrived at this particular expression where the energy per unit length for achieving the minimum delay.

Note that this is the energy for achieving the minimum delay and if I design the repeaters and then the number of repeaters this is the energy per unit length we will be able to achieve. This turns out to be this particular function,

$$\left(\frac{E}{l}\right)_{\text{min-delay}} = V_{dd}^2 C_w \left(1 + \sqrt{\frac{1 + \rho_{\text{inv}}}{2}}\right)$$

If I consider 0.5, I will get this as  $\sqrt{0.75}$ , it turns out to be 86.6% more than that of the  $V_{dd}^2C_w$ . The  $V_{dd}^2C_w$  is nothing but the energy per unit length for a wire without any repeaters. But with repeaters I will get this additional component and especially for the minimum delay, this additional component will be around 86% more.

(Refer Slide Time: 02:47)

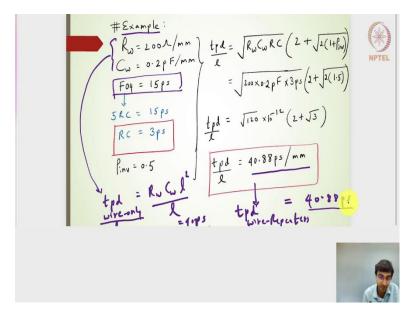

Hope this is just a summary of what we had studied earlier. Let us take an example here. We have a long length of the wire and the resistance and then the capacitance per unit length of the wire is given as  $200\Omega/\text{mm}$  and then 0.2pF/mm. The Fo4 = 15ps for the repeater design.

In that sense on the Fo4 which is nothing but for a unit inverter followed by the 4 other unit inverters we will get the 5 RC parameter as nothing but 15ps. That is what is given

here for that particular chip design. RC value turns out to be nothing but 3ps and they have used the folded technology, the normalized parasitic inverter factor is turns out to be 0.5.

Let us try to determine use those particular expressions which we had seen in the last slide and then see what is the delay, the propagation delay per unit length of the wire, it is nothing but a function of R<sub>w</sub>, C<sub>w</sub> and RC and this is what we had derived earlier. Using this particular expression, if I put in the values of R<sub>w</sub>, C<sub>w</sub> as 200 and 0.2pF/mm, and RC value as a product of RC as 3ps, we are going to achieve  $\frac{t_{pd}}{1} = 40.88ps/mm$ .

Now, this is the minimum delay per unit length turns out to be 40.88ps/mm. If the length is 1 mm, we can get actually the propagation delay of the wire with the repeaters as 40.88ps. Hope this is clear. Now, if I want to find out the delay of the wire without any repeaters, delay of the wire without any segments, without any repeaters, in that sense I shall be using these two parameters because that is the characteristics of the wire itself.

$$\frac{t_{\text{wire-only}}}{l} = \frac{R_w C_w l^2}{l}$$

If l = 1 mm here, in this particular case  $t_{pd}$  for 1 mm for the wire width repeaters. This is an expression for achieving the delay for the repeaters, it turns out to be 40.88ps. In this particular case, if I do that I will actually achieve 40ps.

If I calculate this  $t_{pd}$  of the wire per unit length I will get  $R_wC_wl = 200 \ge 0.2pf \ge 1mm = 40ps$ . If l = 1 mm, I will get the  $t_{pd} = 40ps$ , compared to that of 40.88ps. Hope one should be able to understand if without the repeaters what is the delay and with the repeaters what is the delay.

### (Refer Slide Time: 06:17)

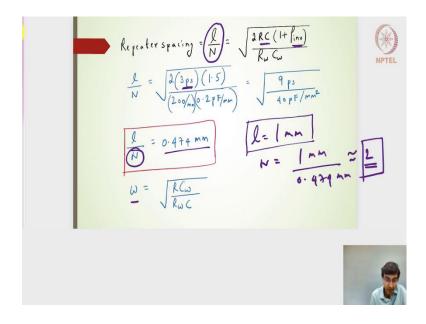

Now, let us try to understand what is the repeater spacing. It is nothing but if we have N - 1 repeaters I will have N segments. I need to find out what is the spacing between the N segments or rather the length between length for the each of the segments. The length of the each of the segments is nothing but,

Repeater Spacing =

$$\frac{l}{N} = \sqrt{\frac{2RC(1 + \rho_{inv})}{R_w C_w}}$$

Rw Cw the parameters are given,  $200\Omega$ /mm and Cw as 0.2pf/mm, that is given from this particular data. Moving ahead RC is nothing but Fo4 is given, I should be able to find RC and that turns out to be 5 or rather 3ps here.

$$\frac{l}{N} = \sqrt{\frac{2(3ps)(1.5)}{(\frac{200}{mm})(\frac{0.2F}{mm})}} = \sqrt{\frac{9ps}{40pF/mm^2}}$$

$$\frac{l}{N} = 0.474mm$$

If the length of the wire is actually 1 mm.

Remember that the number of segments here that I need to introduce the N - 1 repeaters or the inverters in this particular case that has to be a whole number, that could not be a decimal number, that cannot be a real number that has to be an integer. In this case the

number of segments it will turn out to be 2 point something, but it will be rounded off to 2.

I will have to insert 2 or rather I will have to make 2 segments, so that I need to insert one inverter or one repeater for a length of 1 mm, alright. Hope that is clear? Optimize width of the repeater if we have a length of 1 mm then the number of segments is 2.

The number of repeaters I need to add is 1 and what should be the width of that particular repeater and that is given by this particular expression,

$$w = \sqrt{\frac{RC_w}{R_wC}}$$

The Fo4 is actually given as, if I go back the Fo4 is given as 15ps,  $R_w$  and  $C_w$  are given, but I do not really know what is the R value and what is the C value.

(Refer Slide Time: 09:03)

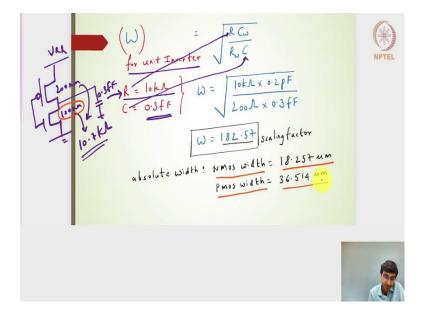

What I am going to consider is for a unit inverter we know that the switching resistance for a unit inverter is close to  $10k\Omega$ . Unit inverter means I will have the PMOS and then the NMOS design. This is a V<sub>dd</sub> and then this is the ground rail. This particular w is nothing but 200nm. This is nothing but 100nm and according to the short channel this turns out to be or even this one turns out to be somewhere around  $10.7k\Omega$ . We know just for our own simplification we consider the switching resistance to be  $10k\Omega$ . The capacitance we consider it to be the 3C capacitance here which is nothing but 0.3fF, where one C the unit transistor, unit NMOS transistors capacitance was considered to be 0.1fF. The 3 times that will be considered for the unit inverter, we will consider 0.3fF which eventually turns out to be RC = 3ps. If I use that particular R and C values here, this R value goes here, this particular C value goes here, we knows what is C<sub>w</sub>, we know what is R<sub>w</sub>, we should be able to find out the optimum width, turns out to be 182.57 the scaling factor.

Now, remember that the w is still a scaling factor, it is not an absolute number, it is not an absolute unit. To find out the absolute width of the repeater or the inverter which we have been using here it is nothing but the NMOS width should be nothing but

$$w = \sqrt{\frac{RC_w}{R_wC}}$$

$$w = \sqrt{\frac{10k\Omega \times 0.2pF}{200\Omega \times 0.3fF}}$$

$$w = 182.57$$

The unit inverters NMOS width is nothing but 100 nanometers here. If I need to scale it by 182.57, then the overall absolute dimensions of the width of the NMOS transistor turns out to be 18.257 micron. The 182.57 x 100nm all also call it as 0.1 microns, I will get 18.257 micron. PMOS width has to be 36.514 micron. The one inverter or the one repeater which we are using for a 1 mm long wire, we need to have the width of 18.257 micron and 36.514 micron. Hope this is clear.

### (Refer Slide Time: 11:35)

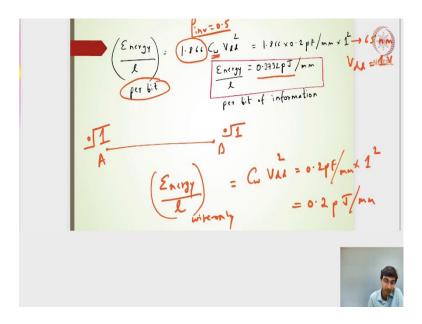

Moving ahead energy per unit length for 1 bit of information that has to be transferred across. If I have a long length of the wire A to B, and I need to have 1 bit of information that is to be passed. The 0 to 1, that has to be passed to the B, B, as 0 to 1, that is what is called as for passing 1 bit of information, what is the energy per unit length of the wire. It turns out to be the expression is  $1.866 \text{ C}_{w}\text{V}_{dd}^2$  as coming from rho inverter as 0.5. If it is a value of 1, it will be different this particular the value will be different, but we have considered the normalized inverter parasitic inverter using the folded technology design as 0.5. We will get,

$$\left(\frac{\text{Energy}}{l}\right) = 1.866C_{w}V_{dd}^{2} = 1.866 \text{ x} \frac{0.2\text{pF}}{\text{mm}}\text{x}1^{2}$$

$$\left(\frac{\text{Energy}}{l}\right) = 0.3732\text{pJ/mm}$$

This is for sending one bit of information on the other side of the long length of the wire with the optimized number of repeaters and with the optimized width of the repeater, right. So, this is the energy that will be consumed, right.

But with adding the repeaters making it an optimized number of repeaters and an optimized width of the repeaters, that we will get the minimum delay, the energy that is being compensated is actually more than 0.2, it is 86% more. Here it is getting to 0.37, here it is actually 0.2, one has to realize that to improve the delay the energy is kind of compromised.

## (Refer Slide Time: 14:07)

What we had seen earlier is just an example for a long length of wire and for getting the optimized design, that we will have a very less delay. What we are compromising is on the energy. We are giving 86% more amount of the energy. There is one more design factor or design fitness we call and that is called as making our designs the number of repeaters or the number of the size of the width of the repeater catering towards the product of energy and delay, that is what it is called as an energy delay product and also termed as

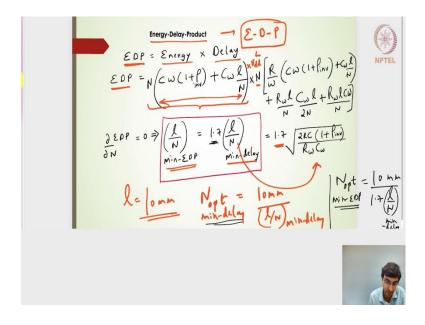

### $EDP = Energy \times Delay$

This is kind of a standard, well accepted, kind of very popular design fitness parameter catering to the digital VLSI design. The other parameter is of course, the delay that is also considered as one of the fitness parameters. Energy is one of the fitness parameters. Footprint of the area is considered as another fitness parameter is the energy delay product.

If I consider the energy delay product for a wire with the repeaters we will have energy multiplied by delay and that has to be optimized now or that has to be minimized, that will get the optimized parameters of w, we will get the optimized parameters of l/N. Then, we should be able to extract what is that propagation delay per unit length of the wire for getting the minimum energy delay product.

Similarly, we will try to find out what is the energy per unit length of the wire with the repeaters for getting the minimum energy delay product. What we had calculated earlier

or what we had estimated earlier was the propagation delay per unit length as well as the energy per unit length, the optimized width and then the optimized l/N catering towards the minimum delay. Now, the same parameters we will try to extract for catering towards the minimum energy delay product, hope that is clear.

The energy delay product is nothing but the product of energy and delay. I should be having an expression for the energy here, I am assuming the  $V_{dd}$  is nothing but 1 volt. I am not written 1 volt square, as I just write it as  $V_{dd}^2$ . This is the number of capacitance we have for the N segments of the wire. If I have a long length of the wire and then make it into N segments, each segment has this particular capacitance.

This is nothing but the wire capacitance and then this is nothing but the parasitics plus the gate capacitance of the next repeater and if I multiply by N, I will get the overall capacitance of the long length of the wire and multiplied by this is the Elmore delay for one segment of the wire and multiplied by N we will get for the N segment, that means, that it caters towards the overall delay of the length of the wire.

$$EDP = N\left(CW(1 + \rho_{inv}) + C_w \frac{l}{N}\right) \times N\left[\frac{R}{W}\left(CW(1 + \rho_{inv}) + C_w \frac{l}{N}\right) + \frac{R_w l C_w l}{N} + \frac{R_w l CW}{N}\right]$$

Once we have the EDP expression and to optimize the EDP or rather to minimize the EDP expression, that we will get the optimized w values, optimized l/N values, we will use a similar differential method. The first order differential of EDP with respect to N is nothing but 0. We will get l/N, expression for l/N, the optimum expression for l/N for getting the minimum EDP.

$$\left(\frac{l}{N}\right)_{\min-EDP} = 1.7 \left(\frac{l}{N}\right)_{\min-delay}$$

$$= 1.7 \sqrt{\frac{2RC(1+\rho_{inv})}{R_w C_w}}$$

If I have a long length of the wire, let us say that the length of the wire is actually 10 mm. The number of optimized repeaters, that I will achieve for the minimum delay here minimum delay, will be nothing but the number of optimized parameters for  $\frac{1}{N}$  will give me the number of the spacing, the number of the length for each of the segments, because N is nothing but the segments.

The N optimized segments that has to be created for a 10 mm long wire to achieve the minimum delay will be nothing but whatever is its value l/N value. I will have 10 mm divided by whatever is the l/N that is been with the optimized parameter of l/N for the minimum delay.

I will get some particular value, if it is 1/N as per the previous example if it was 0.45 or something, I will get N optimum for the minimum delay it turns out to be 10/0.454 slightly above the value of 20. We need 20 more than 20 segments, that is what we will have.

Now, if I use if I try to find out the number of segments for achieving, the optimized number of segments for achieving the minimum EDP. It turns out to be for the same length of the wire 10 mm/ l/N for the minimum EDP which is nothing but 1.7 times l/N for the minimum delay, that is what the minimum delay that is what we had achieved.

If I/N for the minimum delay was turning out to be 0.454 or something like that. In the denominator we have 1.7 more multiplied by 0.454, the optimum number of repeaters, the segments, that we will create for achieving the minimum delay it turns out to be less than that what we have acquired for the number of segments, optimum number of segments for achieving the minimum delay.

For achieving the minimum EDP, the number of segments as well as the number of repeaters will turn out to be less than that of whatever we have achieved for the number of repeaters or the number of segments that we require for the minimum delay. Because this 1.7 parameter is coming into the denominator side and then we will reduce the optimum repeaters for achieving the minimum EDP, hope this is clear and this will be kind of useful somewhere in our design analysis.

(Refer Slide Time: 21:37)

That was about the optimized l/N parameter. Now, let us have a look at what should be the optimum w parameter, the width of the repeater and for doing that we will take the first order differential with respect to the w parameter.

$$\frac{\partial \text{EDP}}{\partial w} = 0$$

$$W_{\min \text{EDP}} = 0.6W_{\min \text{-delay}} = 0.6\sqrt{\frac{\text{RC}_{w}}{\text{R}_{w}\text{C}}}$$

Whatever we had achieved earlier in our previous example of 185.7 something, 0.6 times it will be actually the width of the repeater should be less. Intitually it makes sense because if the width is less the capacitance is going to be reduced and that reduced capacitance is likely to have a reduce the energy term. This particular energy delay product, there is an energy term and not only the delay, only for delay we need to have this w parameter.

Because we are trying to optimize or we are trying to minimize the product of energy and delay and that is why the width of the repeater that we are using has to be reduced. It turns out that it has to be reduced by 0.6 times. If now I have the optimized w and optimized I/N for achieving the minimum EDP what should be the delay, what is the delay per unit length, when we have designed our repeaters and then the number of repeaters for achieving the minimum EDP?

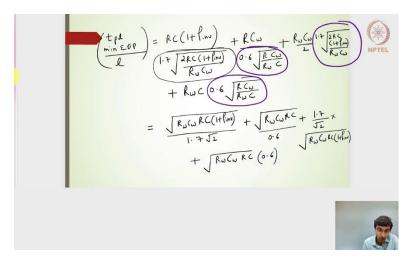

If I put this particular parameters 0.6 and then the I/N which is 1.7 times the I/N for the minimum delay and the similar way what we have done it for achieving extracting the delay per unit length for the minimum delay parameters. We will use the same thing, but just that we will change here the minimum EDP point, I/N and then I/N here and then w here and then w here. Now, this one we will put it for the optimized parameters for achieving the minimum EDP.

(Refer Slide Time: 24:01)

It turns out that the minimum delay per unit length for the achieving the minimum EDP turns out to be, I have written here the expression for the l/N expression for w, expression for l/N here, expression for w here.

(Refer Slide Time: 24:23)

If I carry forward I am likely to get,

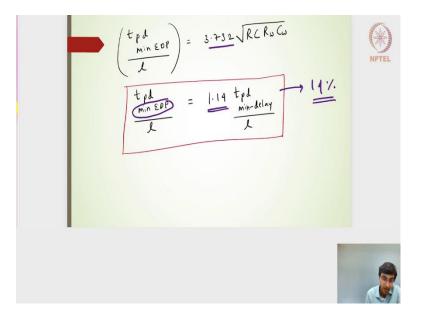

$$\begin{pmatrix} t & pd \\ \frac{\min EDP}{l} \end{pmatrix} = 3.732 \sqrt{RCR_wC_w}$$

$$\begin{pmatrix} t & pd \\ \frac{\min EDP}{l} \end{pmatrix} = 1.14 \begin{pmatrix} t & pd \\ \frac{\min delay}{l} \end{pmatrix}$$

It is actually turning out to be 14% more. If I want to actually design my repeaters and then the width of the repeaters as well as have the optimal number of repeaters, it for achieving the minimum EDP then it will give me the delay which is 14% more, than that of whatever the design the optimized design which will be giving us the delay per unit length.

(Refer Slide Time: 25:07)

If the delay has increased 14% then the energy has to naturally decrease, because we are trying to achieve the minimum EDP point. The product of energy and delay has to be minimum and that is where we have extracted the optimized w and optimized l/N.

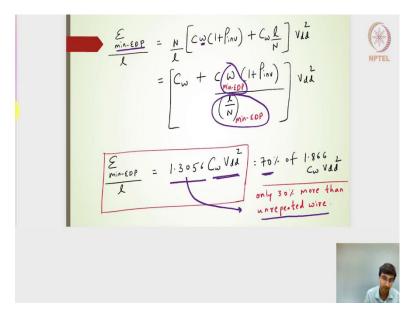

In that case the energy for per unit length for the minimum EDP point, we will try to calculate that which is nothing but N/l and then all the capacitance here  $V_{dd}^2$ . Here the w parameters could be optimized.

$$\frac{E_{\min-EDP}}{l} = \frac{N}{l} \left[ CW(1 + \rho_{inv}) + C_w \frac{l}{N} \right] V_{dd}^2$$

$$= \left[ CW + \frac{CW_{\min-EDP}(1 + \rho_{inv})}{\left(\frac{l}{N}\right)} \right] V_{dd}^2$$

We can put the w optimized parameters for achieving the minimum EDP the optimized I/N parameters for achieving the minimum EDP. If I do that I will get,

$$\frac{E_{\min-EDP}}{l} = 1.3056C_w V_{dd}^2$$

Which is significantly less than that of  $1.866C_wV_{dd}^2$  turns out that it is 70% of 1.866. The 30% reduction in the energy 14% increase in the t<sub>pd</sub>, but 30% reduction in the energy. Overall the product of energy delay turns out to be actually be less.

It also turns out that 30.56, if I compare 1.3056 with that of the wires with no repeaters at all it will be  $C_w V_{dd}^2$ . It is only 30% more than that of the unrepeated wire. Whereas, if I consider this 1.866, it is 86% more. Here its 30.56% more.

Hope you know this the minimum EDP point the important point that to be noticed or that to be observed is that for achieving while we are achieving the minimum EDP point. The delay will increase slightly by 14%, but the energy of the designs of the number of repeaters and then the width of the repeaters it will give us 30 percent reduction from the  $1.866C_wV_{dd}^2$ .

### (Refer Slide Time: 27:15)

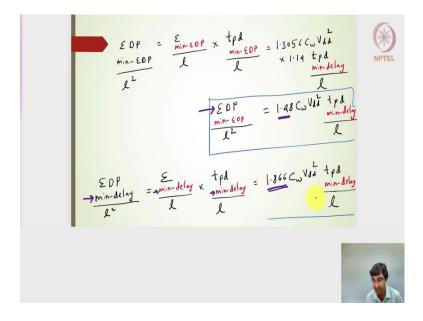

Moving ahead, if I want to find out what is the energy delay product per length square I have written because it becomes easier in our calculation. Energy delay product for the minimum EDP, it is nothing but the energy the minimum energy, the energy while achieving for achieving the minimum EDP point per unit length and then the delay for the achieving the minimum EDP point per unit length it turns out to be 1.3056.

Whatever we have calculated earlier multiplied by 1.14  $t_{pd}$  for the minimum delay per l. It turns out to be if I do multiplication, I will get 1.48  $C_w V_{dd}^2 t_{pd}$  whatever is the  $t_{pd}$  for the minimum delay divided by l. If I want to find out the product of energy and delay for the minimum delay per l square it turns out that nothing but energy whatever we have achieved for the minimum delay multiplied by  $t_{pd}$  minimum delay divided by l and divided by l for both the terms here.

The energy for that we have obtained for the minimum delay is nothing but  $1.866C_wV_{dd}^2 \frac{t_{min-delay}}{1}$ , this factor is 1.866, this is 1.48, and naturally this 1.48 will be less than that of 1.866. That is indeed, what we have in this particular slide what we have validated is the energy delay product for the minimum EDP or the designs whatever we have created for the minimum EDP turns out to be giving the lowest EDP.

When we compare that with that of, there were the minimum delay parameters. The product of the energy and the delay for the minimum delay parameters turns out to be 1.866 and then the other parameters, but here it turns out to be 1.48, naturally it is less.