# Digital VLSI System Design Prof Dr. S. Ramachandran Department of Electrical Engineering Indian Institute of Technology, Madras

# Lecture – 45

## **System Design Examples**

## (Continued)

We were looking at the novel algorithm we have developed for DCTQ quantization etcetera.

(Refer Slide Time: 02:32)

| 1 | 1269   | 4              | -12     | 4        | 1      |           | 5 3  | 1    | 1 | 157         |             |         |      |     | 0     | ī |  |

|---|--------|----------------|---------|----------|--------|-----------|------|------|---|-------------|-------------|---------|------|-----|-------|---|--|

|   | コートレート | 18 9 2 4 0 0 2 | 1429228 | 2222     | 101011 | 101011111 | 9191 | 1001 |   |             | <br>0 0 0 0 | 0 9 9 0 |      |     |       |   |  |

|   | 11.5   | 0 0 2          | 2 0 4   | 10 10 10 | 1 1 2  | 1 1       | 111  | 1440 |   | 8<br>0<br>0 | <br>        | 0.00    | 0000 | 000 | 0 0 0 |   |  |

|   | L      | _              | _       |          | -      |           |      | _    |   | 2           |             |         |      |     | 1     |   |  |

We saw this matrix which is the outcome of the application of DCT on an image block; we have not shown the image block deliberately. For each of these corresponding elements it may be anything from 0 to 255, being eight bit for the actual pixel values. You will normally see some 156, 160 like that all around that may be an average as far as the input pixels are concerned. The DCT is nothing other than the evaluation of three matrices C X and Ct and that gives final result which will be the 8 by 8 matrix shown here.

The very first coefficient, as mentioned, is the DC coefficient and the value is quite high when compared to all other coefficients. That is the reason I said it is 8 times the average of pixels intensities put together. If you divide this by the quantization matrix, for every 8 by 8 matrix you will have quantization matrix; first coefficient will be 8 corresponding to this term and 16 for this, then 16 for this and another 16 for this, then 19, 19, like that it goes 22 and so on until 84 or some such thing. You have to take one DCT and divide it by corresponding coefficient. In this case, it will be 8; so 1260 divided by 8 and after rounding it off, that is, dropping all the fractions what you will get is 157. It is not a rounding off but it is actually truncation.

If you want to recover this what you need to do is just multiply that by 8, this value. What do you get when you get multiply? Do you get it back? No. If you multiply this 8 into 66, I think it is 1256. You started with 1260 but when you reconstruct, this is what is called reconstruction, you do not really recover what you have. Quantization is responsible for this because you are quantizing by 8. That means to say we take only every eighth value. That is why we have in this fashion. This is a lossy process in work and therefore, you cannot reconstruct the actual image but it will be an approximation of the image. On most occasions, it will be quite good. Sometimes you may be surprised to see a very good image constructed.

The purpose of quantization is to create as many 0s as possible as we have mentioned before which need not be encoded in VLC- variable length coding and only these non-zero coefficients are actually coded and converted into serial bit and sent over as a bit stream on the transmission channel. This is just a sample block we have seen here. This is a DCT coefficient as mentioned and this is after quantization. Quantization is nearly division by another constant, a group of constants.

(Refer Slide Time: 05:55)

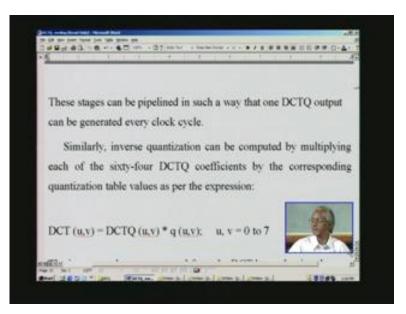

These stages can be pipelined in such a way that one DCTQ output can be generated every clock cycle. I think we have seen this as well and we will see a little more later on.

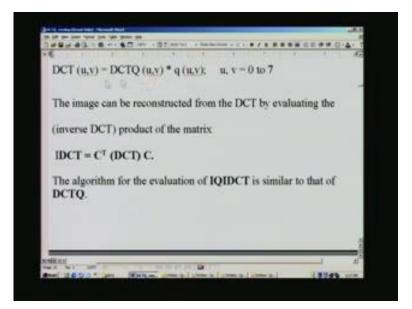

Similarly, inverse quantization can be computed by multiplying each of the sixty four DCTQ coefficients by the corresponding quantization table values as per the expression. This is what we have already explained. Actually this is a quantization matrix, 8 by 8 matrixes. Once again you can see u, v correspond to DCT coefficients earlier. Here we recover the DCT portion. We start with DCTQ and multiply. Earlier we divided by 8 in order to get the DCTQ from DCT; now we have to multiply by 8 in order to get the very first coefficient; similarly, for the other coefficients 16, 19 and so on. We will create the corresponding DCT value here. This is the process of reconstructing the image at the receiving end at the decoder.

(Refer Slide Time: 07:16)

The encoder decoder that we have seen before is also abbreviated as codec. The next step is we still have only the DCT coefficients available; we have not yet recovered the actual image. We can recover it only by doing an inverse operation of this which is similar to DCT, only order has to be C T into the DCT and C. These are all, once again, 8 by 8 matrices, three matrices. The parallel algorithm we have done before is equally applicable for this IDCT as well; out comes 1 pixel per clock. That is the throughput that you can get here. It has to be the same rate as the DCT creation and the same algorithm works too.

(Refer Slide Time: 08:07)

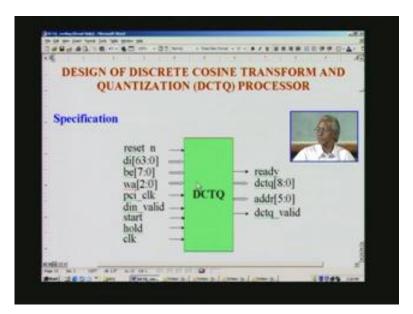

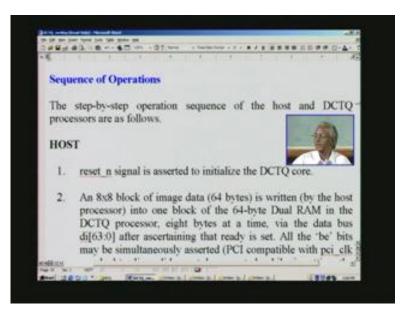

Now we will really start going into the design. Before we design any system that you want to design, you must first have an overall bird's eye view. For example, you ultimately want to do a chip so a good starting point will be to put a block box and then label this. This is the design for DCT quantization as I mentioned here. What we will formulate is this specification. Let us examine what signals you will require in order to communicate the image. For example, I can use a host processor in order to communicate the signal, I mean image. We need a very high throughput so we can think of using a parallel bus such as pci bus which we have already had a glimpse of when we did pci orbiter earlier. We had used any block of image. We can apply one row of a block at a time if you have 64 bits and through pci bus a 64 bit bus will be handy and you can use pci signals. For example, b stands for the byte enable and there are 8 bytes here. Which byte is referred? If you enable that particular byte you need signal. These are all basically pci signals. If you have a core, you need to reset at any point of time. What we have here is reset n and this is standard in any of our designs seen earlier. Once you have this you can communicate the image information from the host processor or from any other processor such as video grabber which we have seen before. Into this DCTQ which is the hardware implementation after going through verilog coding, which we will do shortly.

In order to write different rows of a block; there are eight such rows. So you need a right address for that; three bits are needed for that. You also need a clock such as pci clock. This is the host computer interconnection right from all this. When this data is valid should also be indicated by the host and that is by this. Once you have put in eight rows, you can write it in eight clock pulses using this pci clock. After you have written one block of information you can start the entire DCTQ process. When the DCTQ process is going on you can also input next block of image; this DCTQ group processing there are sixty four coefficients and as I mentioned before you can have one pixel processed every clock equivalent to one pixel process. Thereby, you have a sixty four clock cycle requirement for processing one block; whereas, you need just eight clock cycles as far as pci clock is concerned in order to input here. That relieves the burden of the host processor which is dumping in the image. So it can attend to any other duty other than nearly inputting the information. This is a time consuming operation. I think it is n cube times, n stands for 8 and so many

computations are involved, multiplication as well as addition. You can cross check from the matrix we have seen before.

Once you have loaded the image you can as this DCTQ to start the DCTQ process by asserting this signal. Once it has started, you can hold the processing at any point of time. Thereby, you do not have to bring in what is called latency which I will explain later on if you use hold signal. There is also a system clock required for a DCTQ operation to turn out the DCTQ and that clock is fed here. When this DCTQ is ready to accept input will be indicated by an output signal called ready. The actual DCTQ output after evaluating will be output here and it will be a 9 bit output. This 9 bit output is signed; it will be in two's complement. This is as per the requirements of the JPEG MPEG standards. That is what we said before, right at the introduction, that whatever we design will have to conform to the standards. Otherwise, there is no communication from one product and another product. Which coefficients we are referring to? Is it DC coefficient or the AC coefficient? If so, what is the address? That question will also have to be answered.

The answer is output this address for the coefficient DCTQ coefficient. When this DCTQ is valid? That also has to be indicated by a high going signal. With this you can very well design a DCTQ processor. We have seen all this from a bird's eye point of view. We have also used some of our knowledge about the actual host interface such as pci interface. Once we have formulated what we have briefly explained each of the signals is listed. This is a block diagram of DCTQ.

#### (Refer Slide Time: 13:55)

|       |            | Output | and the first of the fail of the                                                                                                                                              |

|-------|------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| reset | t n        | Input  | Asynchronous, active low.                                                                                                                                                     |

| di[6. | 3:0]       | Input  | One row (8 pixels) of an image block<br>(8x8 pixels) is input. di[7:0] is the<br>first pixel and di[63:56] is the last in<br>the row. A pixel is of size 8 bits,<br>unsigned. |

| be[7  | [0:]       | Input  | Byte enable signal. be[0] selects<br>di[7:0] & so on.                                                                                                                         |

| wa[2  | 2:0]       | Input  | This furnishes the row address of an image block, wa[0] is the first row.                                                                                                     |

| pci   | <u>elk</u> | Input  | Image input synchronous clock.<br>di[63:0] is written into the core,<br>wa[2:0] serving as the address<br>synchronous to positive edge of this                                |

Each of these signals will have to be explained. I will quickly explain because I have already explained. This reset is active low asynchronous which is standard in our design and input is fed through this di 1 row, that is, 8 pixels of an image block; 8 by 8 pixels is input and into this di 7 through 0 is the first pixel and the last byte is the last pixel in the particular row of 8 pixels In a block you have eight such rows. We have to write one after another. A pixel is of size eight bits, unsigned. Note that it is unsigned. This is nothing other than x matrix in that Cx Ct evaluation and so the x is complete only with 8 rights, as such, because every right you write only one row of the block.

You have this byte enable; byte enable be 0 selects di 7 0 and so; on the higher order it is selected by this 7. We have seen this as well. The 0 is the first row address and 7 is the last row address of the block. Image input synchronous clock, that is, the pci clock and all the bits are written using this address serving as the address synchronous to positive edge of this clock. We have to define all these signals. When it really happens, whether it is positive edge or negative edge, whatever the case is we will have to specifically spell it out.

#### (Refer Slide Time: 15:28)

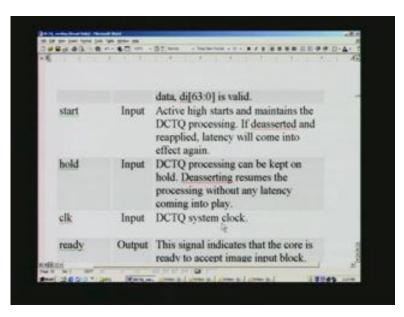

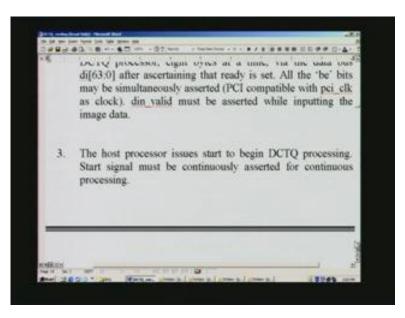

Similarly, data in valid: when the input data is valid. Then we have start signal and whether they are input or output are designated straightaway here. Active high starts and maintains the DCTQ processing. Once you have started, it should not make it low; should keep it high. If you make it low, the whole thing will be suspended and again have to start fresh. Every time you start of fresh, you have to pay the penalty of latency. In this particular design, you will see, later on, that the latency is around 45, which is quite hefty. We will explain why later on. If deasserted and reapplied latency will come into effect again. That is what we are saying. This latency is applicable only for the very first block that we are processing, which is to say, the output starts coming only after the latency time has expired. It will start only after delay. Once it starts, 1 pixel per one clock rate is maintained as long as you do not make it zero. The movement at any point of time you make it 0 again that 45 latency will come into the picture.

If you want to avoid that a better alternative will be to use this hold so that it freezes at the point where you left and you can resume at a later time as the need arises by deasserting the hold. That is what is mentioned here. DCTQ processing can be kept on hold; deasserting resumes the processing without any latency coming into play. Clock is the system clock for DCTQ operation. Ready is the output signal. This indicates that the core is ready to, core, in the sense the DCTQ core to accept image input block.

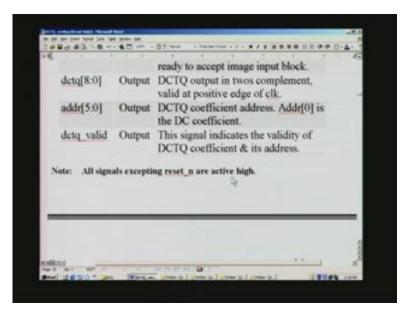

# (Refer Slide Time: 17:08)

DCTQ is the output in two's complement valid at the positive edge of clock. Note that this clock is different from pci clock, that is for inputting the image; whereas, this is outputting the actually churned DCTQ. The corresponding DCTQ address is furnished here; address 0 is the DC coefficient; all others up to 63 are AC coefficients. When it is valid is indicated by this and also the validity of address. All the signals excepting reset n are all active high. This is the standard design.

(Refer Slide Time: 17:48)

|                 | 1 60 m -0   | three is the last of a line |               | # 0-A- 1<br>#2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------|-------------|-----------------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| di[6<br>be]7    |             | do[63:0]                    | result1       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| wa[2            | 2:0]        | multi                       | sux8s result8 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| pci_o<br>din_v  | 11 A        |                             | -U18)         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| rnw             |             |                             | lk            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| clk<br>cntl_reg | [2:0] - m[3 | 2:0]                        |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| result1         |             | 1                           | 6             | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| -               | adder12s    | dctreg2x8xn                 | qr0-qr7       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| result8         | (adder12s1) | (detreg1)                   | -             | 199                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ANRES           |             | r                           |               | interest of the second s |

|                 |             |                             |               | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

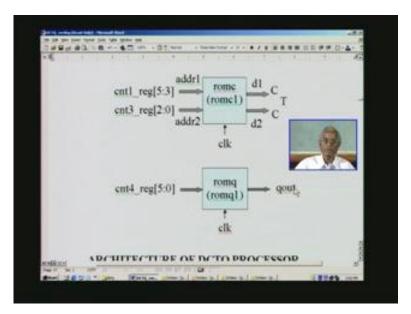

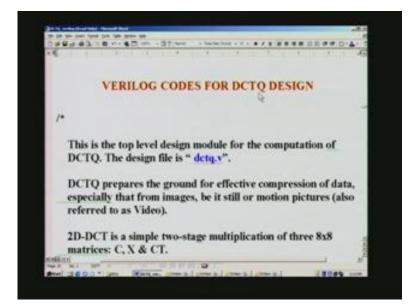

We will have a look into the architecture. The first step is we have to specify what we want. That is what we have done by describing for putting a block and then describing

these signals. They are the basic definitions. Once with this and they are undercurrent for all this is the implementation of the algorithm that we have seen before. That is the crumbs actually. What we are trying do is merely finally turn that algorithm into a chip. Just prior to making the verilog design, we need to put a hardware structure here and this is what is called architecture. The architecture will have to reflect the actual hardware that we need. Let us see.

We have already seen dual RAM designed earlier and that is precisely what we will use here so I will not describe dual RAM except for the signals merely to recollect what we have done before. All these bold notes are the pin configurations that we have seen before. We have seen a block diagram with all the I/O pins there. That is what will be the final IC when you do it as an ASIC or FPGA. Those things are mentioned bold within the architecture because there are so many signals in the architecture. Other than bold, they are all internally created. So it will come from some other module. You have already seen these things before. Input is applied through di and when it is valid byte enable, which row address we are talking about is here, pci clock at the positive edge of the clock we input here. It is a dual RAM

In the sense we have two RAMs. The first block that you have to put in will be put into one of the RAMs, say RAM 1 and RAM 2 is empty to start with. Therefore, DCTQ quantization will not start. After completing the first RAM 1 field, we will give a start signal. That start signal is down below which we will see later on. We have seen up to this. Din valid is the data invalid. You need eight pci clock cycles in order to write one image block. Once that is done, we switch control from one RAM to another. That is done by toggling this rnw; this toggling of rnw must be by the DCTQ processor. This will be the signal internally created. We will see later on that it is coming from the controller of which we will see in the design. This is the system clock.

#### (Refer Slide Time: 25:25)

| result1<br>result3<br>result3<br>result4<br>result4<br>result4<br>result5<br>result4<br>result5<br>result4<br>result5<br>result4<br>result5<br>result4<br>result5<br>result4<br>result5<br>result5<br>result5<br>result4<br>result5<br>result4<br>result5<br>result5<br>result5<br>result5<br>result5<br>result5<br>result6<br>result6<br>result6<br>result6<br>result7<br>result7<br>result7<br>result7<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>result8<br>res | Ba 43 18 40 m -0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 22 feet - a feetheriner + 11 + 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                       | -     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------|

| clk<br>cnt1_reg[2:0]ra[2:0]clk<br>result1sum1dctreg2x8xn _qr0-qr7<br>(adder12s1)dctreg1)qr0-qr7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | almm1) C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Los Las Ma            |       |

| result1<br>result8<br>adder12s<br>(adder12s1)<br>cmt2_reg[2:0]<br>result8<br>adder12s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>adder2s<br>a  | clk →                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | clk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                       |       |

| result8 adder12s<br>(adder12s1) detreg2x8xn qr0-qr7<br>(detreg1)<br>cnt2_reg[2:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | cnt1_reg[2:0] ral                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                       | -     |

| result8 adder12s<br>(adder12s1) detreg2x8xn qr0-qr7<br>(detreg1)<br>cnt2_reg[2:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | result1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                       |       |

| results (adder12s1) (dctreg1)<br>cnt2_reg[2:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 100 million                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | and the second se | 1.007                 |       |

| cnt2_reg[2:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Polya and PM 121 Control of Contr | Detregational .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | edu 2                 |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | (adder[2s])                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | (detreg1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                       | _     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 100                   |       |