Digital VLSI System Design Dr. S. Ramachandran Department of Electrical Engineering Indian Institute of Technology, Madras

Lecture – 39

**Design of External RAM**

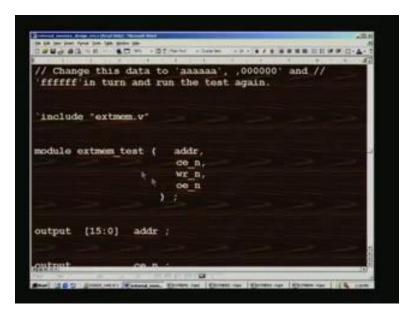

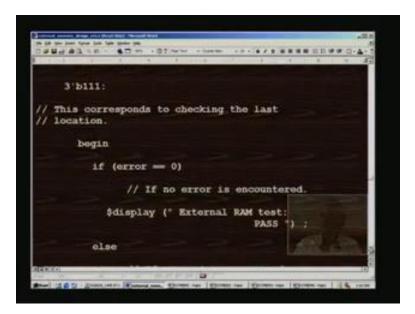

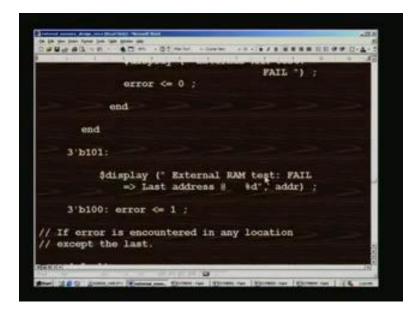

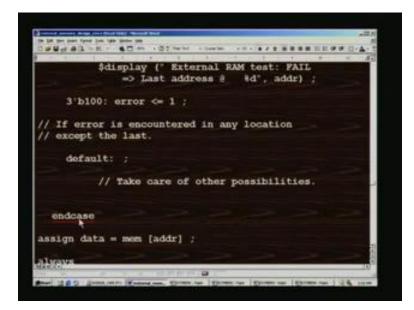

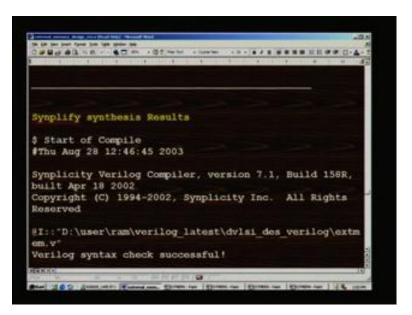

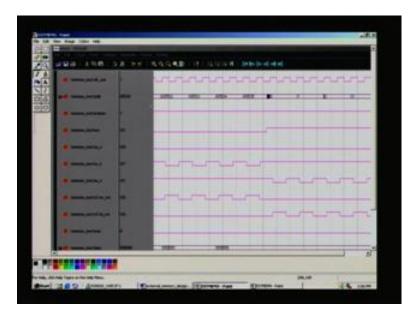

(Refer Slide Time: 01:37)

We are looking into the design of RAM. We have seen how to design a dual RAM which was on chip. That is, it is internal to the chip we are designing, be it FPGA or ASIC.

(Refer Slide Time: 02:24)

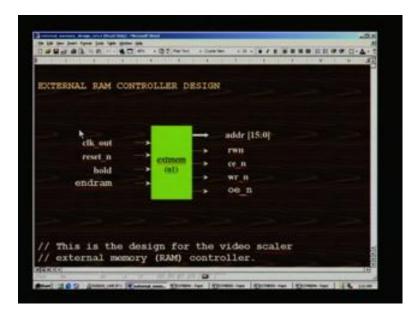

We will now consider how to interface with external RAMs? This is important to locate the RAM externally in some of the applications. For example, for video scaling you require huge memory storage. For example for the picture size of 1600 by 1200 pixels size color motion picture, it would require per frame about 2MB for one color; for three colors, three times of that, so 6MB that will be the size of the RAM that we will be requiring, if you have to store just 1 frame and if you require two frames storage, double that capacity will be required. Needless to say, we need this for such applications RAM which are external to the FPGA or even ASIC. What we have here is a design for such a controller which will connect to the external RAM. Looking at this figure here, we need this controls in order to interface with external RAM on to the FPGA, we will be deciding. This design will be housed in the FPGA or ASIC which we design. Clock out is the system clock for the memory being a synchronous system. There will be a reset as usual and there can be a hold, in order the hold the process. In addition to this, we need enable for the external RAM. What is shown here is only controller for one RAM. In cases like video scaling or data compression we need dual redundant RAM. In which case we need to select this given enable signal as well for that. In addition to this we need two sets like this for two RAMs. These signals are... ce stands for the chip enable; (Refer Slide Time: 04:38) if you have two RAMs, naturally ce<sub>1</sub>, ce<sub>2</sub> you can have. Similarly, this is the write signal for the external RAM; this is the read signal for the external RAM; y is output enable. Normally, the nomenclature used in most of the memory vendors is precisely this. As usual we have one read.

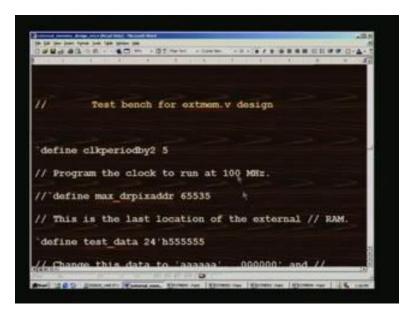

There is a change here we will make read low, I mean read active high and write active low. So, rwn is the one which will select between two RAMs in case we have. In addition to that, it also solves the purpose of telling us whether we are writing into the RAM or reading, we can use in the test bench appropriately here. There is also an address bus for 16 bits. That means it can address an external RAM of 64 kilobytes. For higher memory requirements you need to jack up this here. This is the design for the video scalar external memory, RAM controller, as I mentioned before. This is the maximum number of address location that you will encounter in a 64K, this in decimal here.

(Refer Slide Time: 06:07)

| 0.494.00.         | 8 - 60 m +02 mm + 10+ 17 8 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10101             |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                   |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| define m          | ax_drpixaddr 65535         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| module ex         | tmom (                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                   |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                   | clk out,                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                   | reset n,                   | 100 March 100 Ma |

|                   | hold,                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                   | addr,                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                   | ondram,                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                   | IWD ,                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                   | 00 n,                      | A DESCRIPTION OF TAXABLE PARTY.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                   | wrn,<br>oen                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                   | CO II                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                   | ):                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                   | .5.5                       | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| REAL PROPERTY AND |                            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

We first declare the module for the external memory. This is the control design we are looking into. All I/Os that we have seen on the diagram are listed here, followed by the declaration of I/Os.

(Refer Slide Time: 06:17)

|        |             | + 1    | 4 | <br> |  |

|--------|-------------|--------|---|------|--|

| input  |             | hold ; |   |      |  |

| input  |             | endram |   |      |  |

| output | [15:0]<br>* | addr j |   |      |  |

| output |             | xwn ;  |   |      |  |

| output |             | ce_n ; |   |      |  |

| output |             | wr n : |   |      |  |

| output |             | 00_8 ; |   | 19 2 |  |

This 15 through 0 is for address and all other signals are here. In addition to that we will be requiring, we have assign statements using some of these outputs. Therefore they need to be declared as either wire or reg. Here it is as a register, because its falls as always block with positive edge of the clock.

(Refer Slide Time: 06:46)

| HOP . | 10.14 II 140 II | CURU N  | - 4    | 1/ 4 |  |

|-------|-----------------|---------|--------|------|--|

|       |                 |         |        |      |  |

| rog   | [15:0]          | drwaddr |        |      |  |

| rog   | [15:0]          | drraddr |        |      |  |

| wire  | [15:0]          | drwaddr | next : |      |  |

| wire  | [15:0]          | drraddr | next   |      |  |

| wire  | enva            | ddr ;   |        |      |  |

| wire  | enwr            | ant :   |        |      |  |

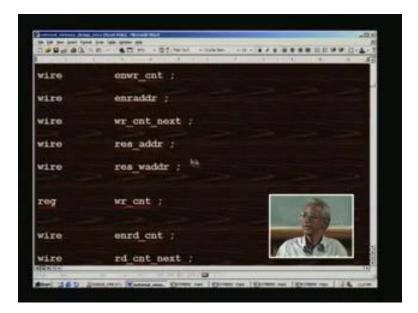

In addition to this we need read address and write address separately for the video scalar. Therefore it has been bifurcated in this fashion. Once again the width is same as the address what we have considered. This is next value; whereas, these are all the registered values.

| 1.0000 | 4 4 4  | HR HEVA   |      | 1.1. | <br>1 4 |     | 1.10 | 1   |

|--------|--------|-----------|------|------|---------|-----|------|-----|

| wire   | [15:0] | drwadda   | next |      |         |     |      |     |

| wire   | [15:0] | drraddi   | next |      |         |     |      |     |

| wire   | оруа   | ddr ;     |      |      |         |     |      |     |

| wire   | enwr   | cat :     |      |      |         |     |      |     |

| wire   | enra   | ddr ;     |      |      |         |     |      |     |

| wire   | WI_G   | nt_next ; |      |      |         | (B) |      |     |

| wire   | res    | addr ;    |      |      |         |     |      |     |

| wire   | res    | waddr ;   |      |      | 1       | 10  |      | - 1 |

(Refer Slide Time: 07:10)

Similarly, there will be one for address write; there will be one enable signal internal use. Since we are using external RAM, we will not be in a position to achieve that high speed that we can, with the one chip RAM. For example, you may have to scale it down by a factor of 2. For instance, if you are operating the system clock at 100 megahertz, we can access external memory only at 50 megahertz rate. In order to do this one, we have a counter here the counters are separate for read as well as write. In order to enable that counter we need another signal and they are all assign statements. That is what and in addition to this for write address we have a read address. Similarly, write count, next also is required in the course of before registering.

(Refer Slide Time: 08:02)

We also have some resetting the address and resetting write address similarly for other signals.

(Refer Slide Time: 08:12)

| wire     | res_waddr ;                        |

|----------|------------------------------------|

| reg      | wr ent ;                           |

| wire     | enrd_cnt ;                         |

| wire     | rd_cnt_next ;                      |

| reg      | rd cnt ;                           |

| wire     | res_raddr_:                        |

| assign r | es addr = (addr 'max drpixaddr)6 : |

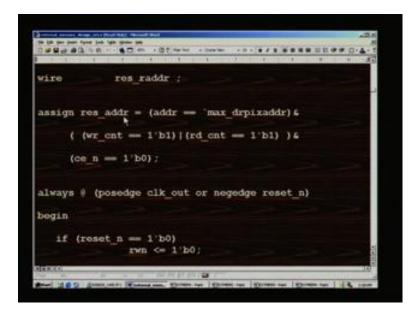

Such as write counter is registered; enabled read counter; its next value; read count itself here. This is enabled. This is the actual counter (Refer Slide Time: 08:25). It is only a single bit counter, it just counts zero and one; it is nearly a toggling flip flop. We have further read address reset as well.

(Refer Slide Time: 08:45)

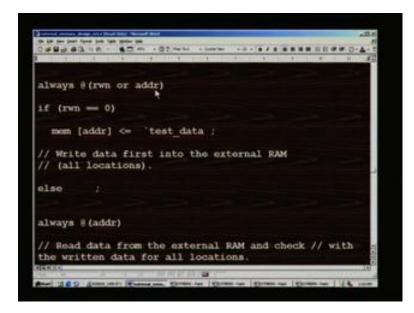

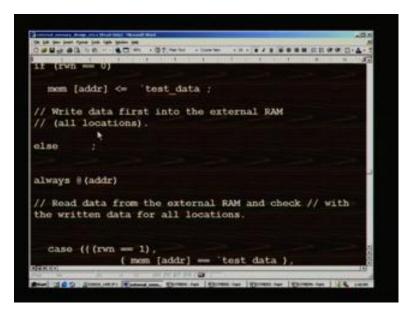

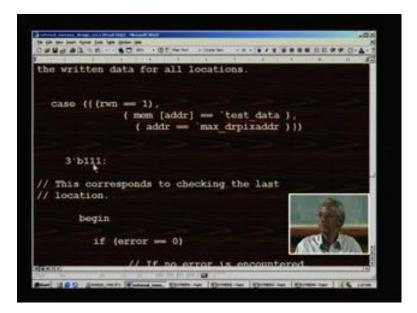

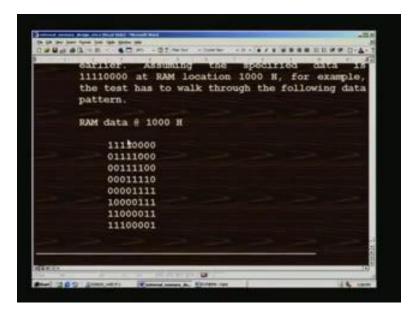

We will have a look into the actual Boolean expressions that we need to evaluate for achieving this. First is the reset address, whenever you want to reset the actual address, we have to look for is whether we have already processed all the addresses write up to the maximum. This is the 6 5 5 3 5 in this case and when it matches with the current running address. Then if the write counter or the read counter is 1. As I said before the write counter is to scale down the speed of the access memory access by 2. That is the reason why we have one bit counter for separate counter for write as well as read. Whether this counter is 1 or this counter is 1. It will go from 0 to 1. It starts with 0, so we take every alternate clock only we need to process. Together with this we also need a chip enable and when it is enabled only then we reset the address. The address resetting means, when it touch the running address will be from 0 1 2 etc., 65 535. When it touches 65 535, then this signal is created.

(Refer Slide Time: 10:01)

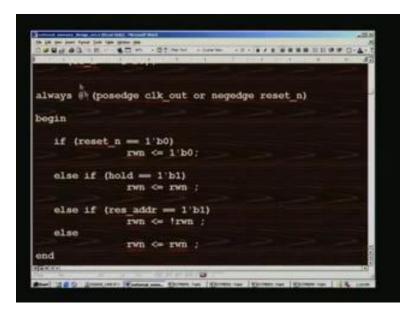

We have one register here, for creating this rwn, which we have seen earlier and this is meant for whether I mean selection of read or write. For example, if it is 1 it will be a read; otherwise it will be write. As usual we have taken for reset hold condition and what we should do? This is initialised to 0 here at the power on reset. When reset address is encountered what we need to do is, just change this rwn and invert it. Because we can access the next external RAM in the case that we have dual RAM.

(Refer Slide Time: 10:50)

We need an enable for write counter and that is derived from the enable RAM being high and rwn being low that corresponds to write here. That is why we have a write counter here, also ce must be activated, that is ship enable must be activated.

(Refer Slide Time: 11:11)

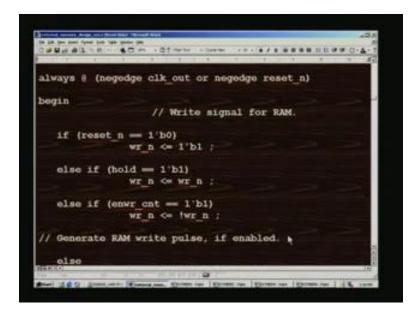

In this always block, note that, we are creating at negative edge; all along we have seen at positive edge clock. We also use the negative edge clock here, in order to create address at the positive edge of the clock and following negative edge this write pulse is issued. When a write pulse is issued the address is always stable that is the reason why we have design in this fashion. That is the reason why we need a negative edge of the clock here. This creates the write signal for RAM. Once again these are all the usual reset and hold and so long as it is enable as we have seen before. What we need to do is, invert the write. If it is in... the write pulse is not there that is, active high it is not active high it is a high position. We need to clock it I mean make it low. That is possible by inverting here. If it is already low with the arrival of the next clock pulse at the negative edge this will go high again. Thereby you create at every two clock cycles one read write pulse which is active low.

(Refer Slide Time: 12:29)

| reformed partners device (Accel Read Read Read)        | 1.000  |

|--------------------------------------------------------|--------|

| te gat her part formt hat fabr preise par              |        |

|                                                        | 00.4.1 |

|                                                        | 1 14   |

| wr n <= iwr n ;                                        |        |

|                                                        |        |

| // Generate RAM write pulse, if enabled.               |        |

| A denerate way write hurse, it energy                  |        |

| 14122                                                  |        |

| olse                                                   |        |

| wr n <= 1'b1 ;                                         |        |

| Construction of the second second second second second |        |

| // Otherwise, disable <sup>5</sup> write pulse.        |        |

|                                                        |        |

| and                                                    |        |

|                                                        |        |

|                                                        |        |

| assign wr cnt next = wr cnt + 1 ;                      |        |

|                                                        |        |

|                                                        |        |

| always # (posedge clk out or negedge reset n)          |        |

| really : (beneadle ers one or underde reace ut         | - 1    |

| 4814                                                   | 1      |

|                                                        |        |

You just take it to the safe state of 1, being active low here.

(Refer Slide Time: 12:36)

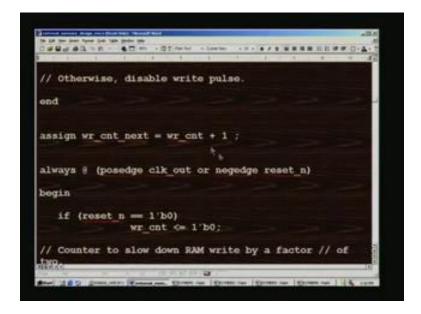

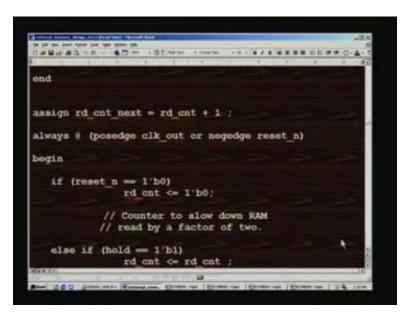

Then what we need to do is, increment the counter and this is advance increment. In this always block at positive edge again here. What we do is we reset the counter to start with.....

(Refer Slide Time: 12:53)

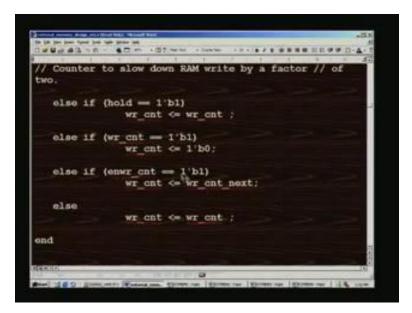

When write count is 1. That is counter is running between 0 and 1. Whenever it is 1, that is, the identification of the second clock, only then write count will be force to 0. That is why it is going from 0 to 1. So long as that enable is activated it will keep counting. That means, to say it counts from 0 and 1. Similarly we will have a read counter it is exact counterpart. I do not have to explain it length, that one.

(Refer Slide Time: 13:30)

| 10000  |                                                   |

|--------|---------------------------------------------------|

| assign | drwaddr_next = drwaddr + 1 ;                      |

| assign | enwaddr = (endram == 1'b1)6                       |

|        | (rwn - 1'b0) 6 (wr_cnt - 1'b1) 6                  |

|        | (ce_n == 1'b0);                                   |

| assign | res_waddr = (drwaddr = max_drpixaddr)&            |

|        | (wr_cnt = 1'b1) & (ce_n = 1'b0) ;                 |

| always | <pre># (posedge clk_out or negedge reset_n)</pre> |

| hegin  |                                                   |

Before that, we have write address generated here; this is advance increment here and we increment only with this enable signal here. That is enabled only if that enable RAM is activated and read write is in write mode, so wn here. Also write count is 1 that is the second clock only we process. Further you need chip enable active here and there is also a reset write address and which again is depend upon the maximum value of the address. That is encountered for write address. Once again that write counter 1 and c is also taken into account here.

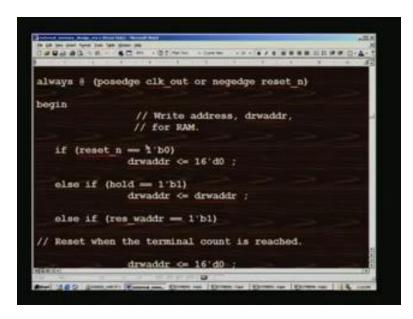

(Refer Slide Time: 14:21)

In the next block, we process the actual that is only an assign statement earlier. What we do is? We really process only here, based upon the reset write address and we have seen there.

(Refer Slide Time: 14:37)

We reset the address, because it has touch 65535. We need to reset that one. It will be resettled at this point of time. As long as the enable is on, which we have seen the condition earlier. Write address is incremented this also we have seen in assign statement earlier.

(Refer Slide Time: 15:00)

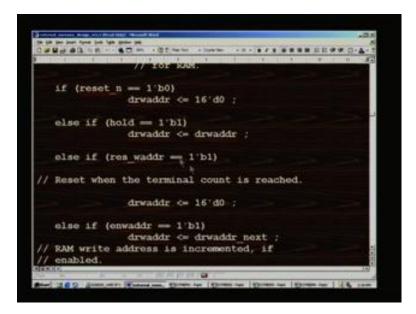

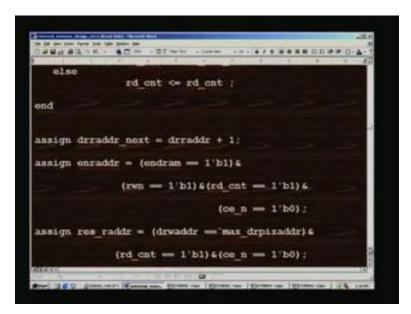

Similarly, we handle the read counter as we have done before for the write counter. It is precisely the same except that write is replaced by read and this is advance increment.

(Refer Slide Time: 15:16)

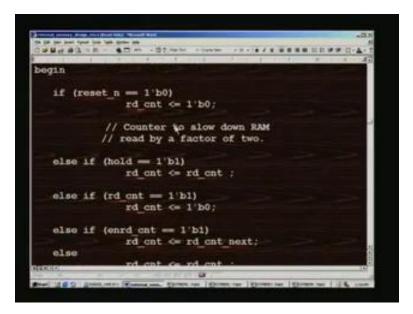

Actual read counter is processed here. As long as read counter is 1 only then it is it is made as 0. That is, 0 is made 1; 1 is made 0 and so on, keeps on toggling by these two expressions here. It is exactly the same as write counter.

(Refer Slide Time: 15:32)

Once again assign statements are there for read address and it is exactly the same as write address, we have seen before. Exactly matching condition except for the fact that read is 1. That is in read mode. Earlier it was 0 for the write address.

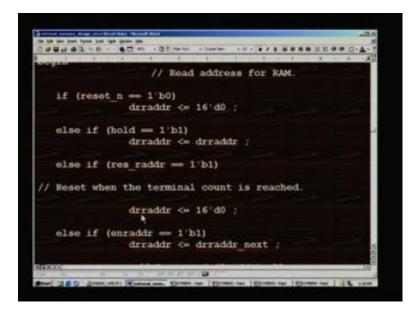

(Refer Slide Time: 16:10)

In this block, we actually take that assign statements, intermediate results and then process accordingly. For example, when the terminal count is reached it is reset here and otherwise it is incremented here (Refer Slide Time: 16:14), advance increment was shown earlier. If none of these conditions are satisfied we simply write it back to the same thing that will not disturb the contents.

(Refer Slide Time: 16:29)

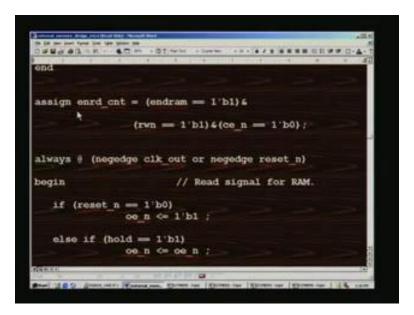

We have an enable read counter and that is based on enable RAM being high and read write is in read mode and chip is enabled. For this condition, what it does is, read signal for RAM.

(Refer Slide Time: 16:45)

| n hit me peer speer link title prote of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| the local day in the local day is a second day of the local day of the local day is a second day of the local d | to additional and the second s | A LINW C-A- |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |

| always 🕴 (negedge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | o alk out or negedge reset n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0           |

| oogin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | // Read signal for R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | м.          |

| if (reset n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1'60)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |             |