Digital VLSI System Design Prof. Dr. S. Ramachandran Department of Electrical Engineering Indian Institute of Technology, Madras

> Lecture No. # 35 Xilinx Place and Route Tool (Continued...)

(Refer Slide Time: 02:33)

(Refer Slide Time: 03:20)

(Refer Slide Time: 30:31)

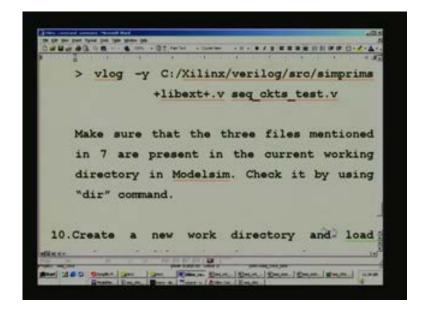

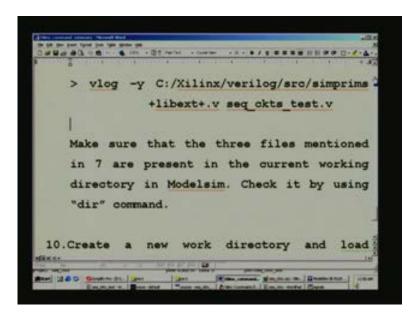

..... "seg ckts banno.v include Xi1 library and back annotated the command vlog -y C:/Xilinx/verilog/src/simprims +libext+.v seq ckts test.v Make sure that the three files mentioned

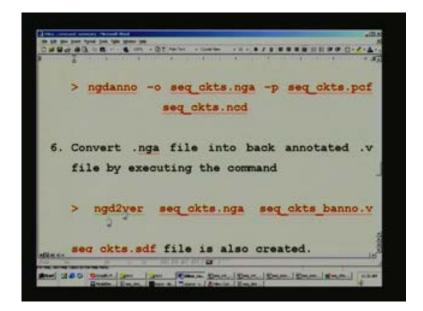

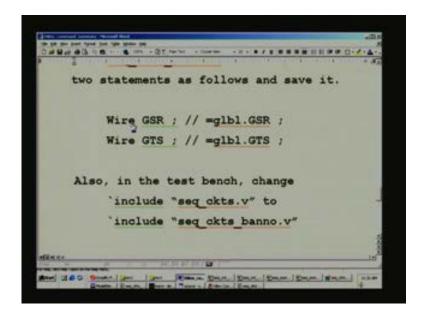

So far we have seen how to back annotate design files by using primarily two commands: it is a ngdanno and this the output option, and these are all, this is the output file and input file being this and which was obtain by xilinx place and route. Then final back annotated file, which is sequential circuits underscore banno dot v which we gave and was derived from the input file nga which is the output of this first phase. You need ngd2ver log conversion to do effect this back annotation file and a standard delay format file was also created, and then, we also saw that we need to replace some two statements by commenting out this two here, as shown here.

Now, in the test bench, we should make sure that this back annotation file is added in place of dot bm file. We had used earlier for the optimization, and that is, I think this they want. So, if I will just increase the font size for this, so, we can see this. So, include sequential circuits underscore banno, I have already done this, and with this will be running.

So, now, next step, let us see, will just follow this is to compile. Before we compile, we will have to open the modelsim. The primary goal is to back annotate, and get a file back annotated file. This is very much shocking to the source file, your design file, and this file, will have to be taken into the modelsim and simulated. Make sure that after back annotation, the gate delays take effect that is the primary purpose of doing this. In order to do this one, let us open, I mean, if modelsim is, I think is already open here, and so, we had to key in the command here, and that has also been done earlier. I will just show.

Command that we have to give is, vlog is another command version. This is the promp;t it is like a Unix prompt and inside the modelsim window and vlog is one which recognizes as a compiler. What we have to compile is library file because after back annotation, we will get all the primitive cells coming into this file.

So, basically the mugs - LUTs - which I had told you earlier and these primitive cells will get reflected into this file. If you open out back annotation, you will precisely see this, and you have to compile that file, that is, this file is actually inside a test bench; that is what we have to already seen some time back, and wherein, we saw that this the one, this is the test bench actually. In that we have added included back annotation file instead of dot bm file which we did for optimization earlier.

Now, in addition to this test file which contains the back annotation file, you have also to mention some library files required for recognizing the modules of the primitive cells, etcetera. They are all basically modules and they will be recognized and or located in the xilinx path where it is the primary xilinx software is loaded and that entire path will had to be given here, and include this library there. So, this includes all the primitive cells library; along with that you have to compile, and of course, your back annotation file: when you run this, it does the compilation.

(Refer Slide Time: 06:47)

(Refer Slide Time: 06:53)

---and annotat saf bench, seg ckts test.v into the 8. Edit seq ckts banno.v file and comment out statements as follows and save it. Wire GSR ; // =glbl.GSR ;

And after this, we had to make sure that the three files mentioned in seven, that is previous step we have done here, that is here, we had a dot v back annotated file, then sdf file and as well as your test bench which is edited for including back annotation file. So, this things, three files are what is referred here, that is what is referred here, and check it by using, you can use a directory command to, see, make sure that these files are present, otherwise, you will get an error if one of the files is missing.

(Refer Slide Time: 07:27)

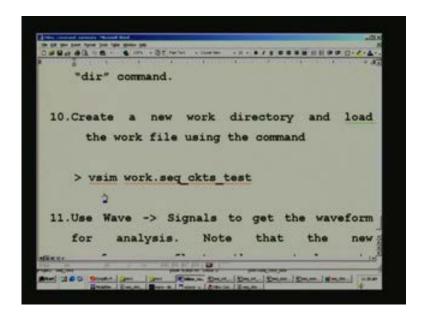

Next step is we will see this step and then go to the modelsim in order to do both. It is basically two comments that you have to execute in the modelsim prompt. Next step is, suppose a new directory is not created already, you may have to create a work directory there that is what it says here. Create a new work directory and load the work file using the command vsim.

(Refer Slide Time: 08:25)

#### (Refer Slide Time: 08:54)

Vsim is the one command for the stimulation and its actually for loading the design file because we have compiled with the back annotated file and that corresponding file will have to be loaded. That is what we say, whenever you have a compilation, it should be followed by simulation, and that is what we do here and naturally that is in work directory and the name it has is precisely same as your top module which is the test bench, which includes the back annotated file.

So, we will do this together and we can even finish the last step. You can use as usual wave signals in order to see the waveform for analysis, and since there is a difficulty in you viewing this on the TV monitor, we will as usual show it on paint and note that the new waveforms reflect the actual gate delays being the result of the back annotation. So, this is what you have to bear in mind. So, now, let us see the modelsim window, that is here, so, those first is compilation, this has been already keyed in here, and this vlog minus 5, all that what we have already seen and sequential circuits underscore test dot v.

## (Refer Slide Time: 09:13)

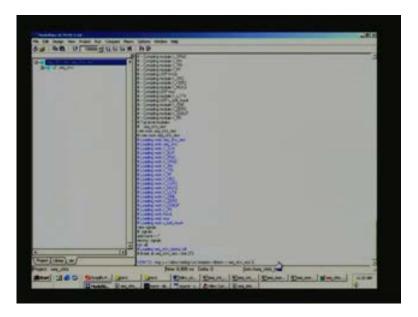

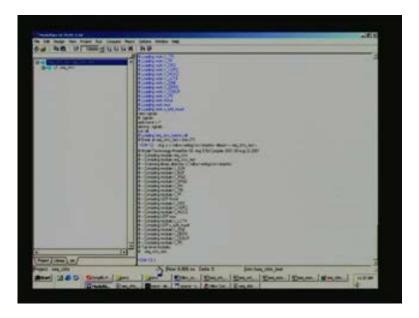

So, let us execute this just give a return. So, it has done the compilation. During the compilation it say, I mean it reports compiling module x underscore buff, then i pad o pad invert tri-state buffer flip flops or gate exclusive or mugs and so on.

So, this is as a result of including the entire xilinx library as such here, and thereafter, you had to have the test bench also compiled and that is already done here. Prior to this it compile's your design actually; this is a back annotated design and this back annotation is not specifically mentioned because what we had declare as a module is actually sequential circuits in the design. So, we did not change the module name; so, what it reports is only the module name as you see here. So, it has successfully done the compiling work now. So, what the next step is to load this file.

# (Refer Slide Time: 10:27)

This is vsim work dot sequential circuits underscore test. This has loaded once again you can see the i pad o pad all are reported here; it is loading module by module; each one is called work directory, and along with the extension, whether it is a test bench, or the design or the library here. The next step is to see the wave form, so, which we can use view, then signals, and then, when the signals window opens, then use view wave; then the last option is signals in design.

(Refer Slide Time: 11:09)

## (Refer Slide Time: 11:45)

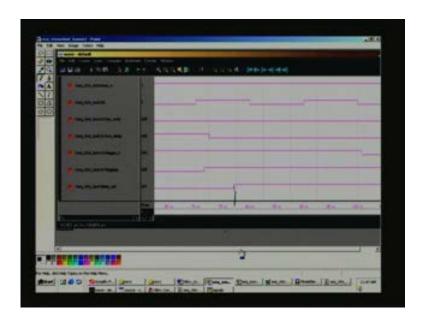

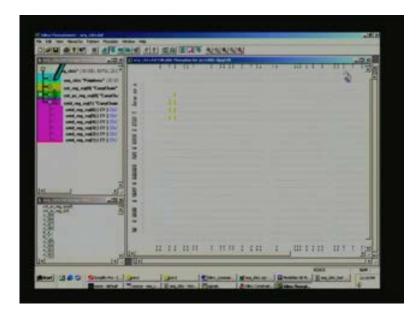

So, this is what you are already familiar and it is already open here. So, now, what we need to do is run this. So, it has run and once again this is crowded here, we can't make out anything here. So, what will do is I will directly open some of the examples; I will consider a couple of examples in order to explain the result of back annotation.

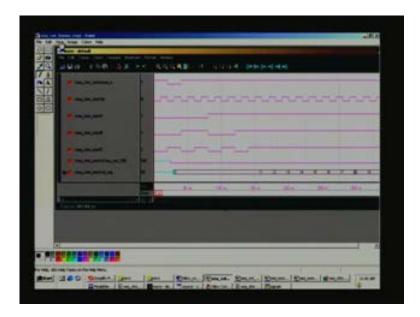

So, as I mentioned earlier, the gate delays must manifest here in the wave form. Let us first open what is called as sequential counter which we used for the after optimization; we saw small delay and this is what it is. Before zooming in, I will just explain what it is. The whole scene is available in just a single page.

So, you can seek here a counter reg being reset 0 corresponding to a reset been here and you note that reset happens right here, whereas, only after delay, this 0 has been reset. So, earlier it was not the case. So, probably in the optimization, even in that phase, I think you did not get any delay as such. There was a delay in somewhere else; so, may be when the counter started. Now, if you see here, this is the positive edge pulse here of the clock, and the actual counter advances not at that one, but only after delay. For example, this may be around two nano seconds or so, and every count is always a delayed by the same amount. Once again you can see here as and it is counting from 0 1 2 3 and so on, right up to 9.

So, we will see one more view of this towards the end of this count. So, the counter is, I mean it counts from 0 to 255 in steps of 1 and then revolves back and it keeps on going like that in a cyclic fashion. There are other signals which we need not really worry about because we have already seen couple of times earlier. So, these are all to advance the counter, then reside the counter using inputs here. I will first zoom, so that you can clearly have a look.

So, we can see reset clock a b c as input here and finally a reset count. Here, you can see that after back annotation, I could not find reset count as well as advance count. Advance count is totally missing, as I mentioned it was used in other circuits. So, naturally that got drop because similar such signal was there and some other name. So, at the time of optimization after synthesis itself, it was missing advanced count, and here also it is not to be found after back annotation, and here reset count also got changed little, so, it has renamed as some 199.

So, it takes some more detailed manifestation here as far as the signals are concerned, I mean, in the sense, if it is a multibit, where it reported as one group earlier. In this back annotation, will, it will separate out all the signal's and report separately and it will be very tedious for you keep track of the count, etcetera. So, we may not be in a position to see the actual count value in some cases, perhaps we are lucky to see here in this case, back annotated file only, as the name implies here, and opening this one, the count goes in this fashion 0 1 2 3 and so on. You can see a b c becoming 1 that is the condition we set for the counting to start and that is precisely where it has happened. Now, we can have a look at the difference. See, here, the positive edge of the clock occurs here; where as the actual count takes place only here.

So, this is clearly due to the gate delays associated with the circuitry for that particular path, and so is the case, we can see equal amounts it is shifted from every clock here, and clock frequency is I think same 20 megahertz, I mean 50 megahertz, 20 nano seconds I think.

So, we will open another, this is going right up to 10. So, we will continue towards the end we will see. So, that one is here and you can see 250 251 and a b c inputs are continuing to be one and reset count is active only here at the time when it is 255. You remember that reset count is basically an assign statement earlier and that will have to

get reflected the moment 255 is encountered in the counter register. What surprising think here is, it is happening in advance.

I cannot offer an explanation, may be there is a bug in the software. So, probably we may have to write to the modelsim and find out why it is so. That is not a serious thing, its happening in advance here, both the edges you can see here, but any way the counting go, I mean after when this pulses encountered, it has to clear and that is what is happening here. You can even see here, some changes here; before going to 0, it goes to some different values, but finally it settles down. So, if i zoom, we may be in a position to see little better.

(Refer Slide Time: 17:33)

# (Refer Slide Time: 18:00)

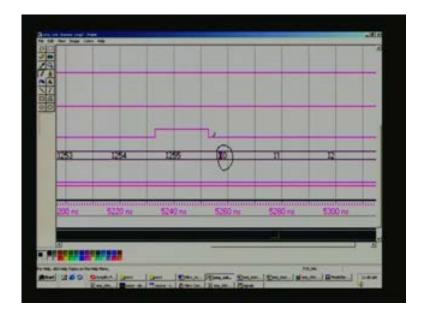

So, we can see 250 251, etcetera. This is the counter reg here; and you can see that pulse here; and you can see this activity here, some ringing like thing. In fact, it is changing to 2 3 different values and finally settling down at 0. That is not a handicap because this 0 will be sensed only at the positive edge, when it is stable. That is what the synchronous circuit is all about. In addition to this, we will see one more example, that is we have seen a mono shot vibrator, and here, it is too crowded, we may had to going to the searching for all the signals, and any way, you would not be in a position to see that is why we are seeing that paint zoomed version.

(Refer Slide Time: 18:15)

So, will now see, there are two more couple of wave forms for the mono shot. This is, here, in mono shot, we have once again a reset, then clock, then reset for the counter. The counter is c n t d here, and as I mentioned earlier, some of the counters are totally separated out. If it is, I think this is 16 bit counter, is it? If it is so, you will get all the 16 signals listed; you may have to manually group them. That will be very tedious; that is the reason why I could not show you a counter here.

So, that is not a handicap because what we are really interested is the final output itself; this delay out is the final output. We have trigger p trigger c, based upon 0 1 condition, we set another signal called run delay, which is, which simulates this short pulse of the mono short. So, it is high here; and goes low here. So, when it becomes high somewhere here, probably just before I should have captured one more on the left, but that is not a major issue. So, what we are concerned is the only delay out which is the required mono shot operation that we are looking for. So, the idea is we give a pulse for, a short pulse for the mono shot and the timer runs and it starts running right at this point. If you see here, it is 75 nano second. This is precisely at 77 here, and you just remember it is 77 here and it keeps on, it is high here and I will zoom this.

It is 77 here. This a fourth point here. So, that means 2 nano second 2 plus 75 77 here, and towards the end let us see. This is the delay out that we have; this is the decide output, and after giving the trigger, it goes high here. Naturally only after the second clock pulse, it will start. All that we have already seen, so, we do not have to see that. In addition to that gate delays also became operational because it is a back annotated file. Therefore, it is much longer it is taking, and only here it goes. In spite of the fact that clock is somewhere way off, somewhere here, this is a clock, and we will go towards the end of this delay out and that is there in the second.

Towards the end, I will zoom here. It is around 5 1 8 0. We started with 77 nano second remember, so, the difference is 5 1 8 0 minus 77. If you take 77 as 80 5100, and 3 extra we had taken.

So, it has given a time delay of 5 1 0 3 nano second. Now, as per our program, it was setting of 255 and we also saw that clock is 20 nano seconds. So, 255 into 20 is 5100. So, if it have the timer had run precisely, it would have made 5100 exactly, but unfortunately we have some 3 nano seconds extra here. So, that is the accuracy that you can have in

this design. This inaccuracy is created not by us or by our design, there is no design flow such, and the basic thing is the path delay has made all the difference. So after all delay out is depend upon to start with, when it is switched, it may have one particular delay; it may have to go through set of gates, and when it is switched off, it may have to go through another set of condition. So, that means another set of gates is coming into picture. So, but in this two sets, whatever is the propagation delay difference, will manifest as the error. So, and that is what you have here three nano seconds explained, is it clear?

(Refer Slide Time: 22:43)

BT P ----the work file using the command vsim work.seq ckts test Signals to get the waveform the new the actual gate reflect being the result of the back annotation.

(Refer Slide Time: 22:54)

#### (Refer Slide Time: 22:58)

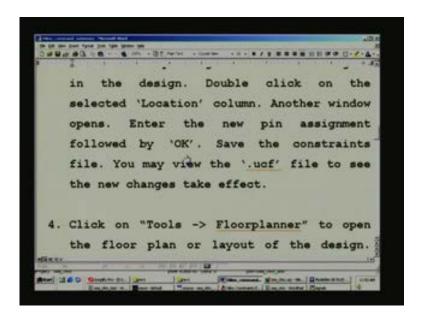

- 02 furbet + tareter + 2 + 8 / 9 8 8 8 8 11 11 10 10 10 - / along with documentation. change constraints such as clock speed pins, click on Tools -> Constraints and Editor. A window opens. Click on 'Global' view 'clk'. For change of 'clk' from 100 MHz to 50 MHz, replace '5' in 'Period' nn to '10' and 'Enter'. For change of click on 'Ports' and in 'Location'

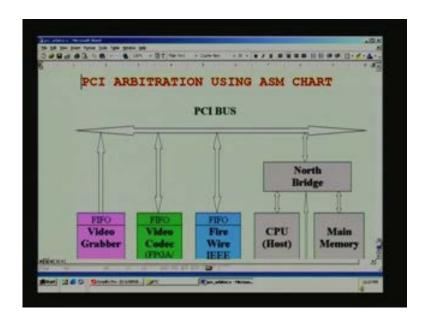

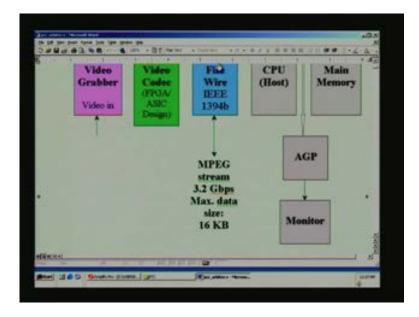

So, this completes the back annotation. So, what we will do is, next is, we will go back to that xilinx command summary. That is what we have seen using wave signals; we have seen the back annotated files. So, what we have done? I have forgotten two other aspects earlier, that is we have been handling constraints. I mentioned that we can take the constraints straight away from a file and open one dot ucf file, and so, will have little more insight into this constraints because this is an important thing that we may to have to handle quite frequently, if you want to make better timing closures, that is, if you want speed of operation, you may have to have all this, you should know, otherwise, you cannot try to get a better speed of operation.

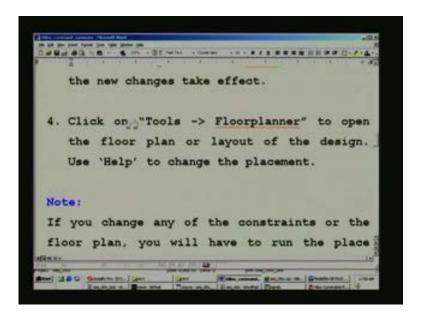

So, I will just go through this. So, first is we will change the constraints for, there are basically two constraints: one is clock, other is IO pins actually. We are dealing with FPGA design, so, we are going to have a peep into how your design has been mapped into the FPGA that will be seeing. Before that, will see what a clock constraint is; how to give this; I will just read out this. To change constraints such as clock speed and pins, click on tools constraints editor. This is naturally in xilinx place and route we have to do this. A window opens, click on global to view clock, and for change of clock from 100 megahertz to 50 megahertz, so, we have programed it earlier for 100 megahertz. So, naturally, half time is 5 nano second; 10 nano second will be the time period, so, half time is 5 nano second. In clock, if you remember in ucf file, that is what we have given - 5 nano second, because it is, as a result of which, we had 100 megahertz, and actually,

this has been taken through the simplify tool - synthesis tool - there in we specify 100 megahertz. So, automatically that has been taken in to account.

(Refer Slide Time: 25:06)

- IST Partiel ..... A window opens. Click on 'Global' 'clk'. For change of 'olk' from view 100 MHz to 50 MHz, replace '5' in 'Period' mn to '10' and 'Enter'. For change click on 'Ports' and in 'Location' column corresponding to the desired signal design. Double click the on lected 'Location' column. Another window pin the opens. Enter new assignment 1000

We change this parameter here to 50 megahertz, that means 5 will have to be changed to 10 or any other thing you can change, and see, whether it is get reflected. Then replace 5 in period column to 10 and enter. For change of pin that is for change of clock, and in the same window you have one more option called ports. For change of pin clock on ports click on ports and in location column corresponding to the desired signal in the design. This, I mean all the signals in your design will also be listed, and identify the design I mean particular signal that you want and then click on that, the location. Double click on the selected location column. Another window opens. Enter the new pin assignment followed by ok. Save the constraints file. We may view the dot ucf file to see the new changes take effect. After this dot ucf file would have been rewritten with the new constraints that you have taken.

(Refer Slide Time: 25:36)

And after that we have one more what is called floor plane. You can actually see where your circuit is residing. So, you can have in terms of the primitive cells we have seen earlier that also we have look, and before that, let us have look at the constraints first.

So, we have, this is the constraints window, and before opening this, I will, this is the xilinx window already open. You remember we had seen this earlier, and it is this version that we are version 3, revision 1. It can state away from the synthesis, just simplify synthesis. Now, what we need to do is we go for tools, and then, in this you have what is called consent editor.

So, when you click on that, it opens here, and if you click on this, you have ports here and you have another thing called global here, and it is, here you have to mention what it is listing is actual clock here and this is 50 nano second high it says and I had change in between, that is why it is like that. Now, I will change back to and actually this 50 nano second is reported here. If i change the i, I will remove that one and it is 5 here. Just enter, that is what we have there on that commend summary, and immediately this 5 nano seconds has taken effect here, and so, next thing is, that is how you change the frequency; you do not have to worry about any other thing nano second high 50 percent; it is 50 percent due to cycle it goes from 0 to high and that is what the clock is for and clock is listed here. All other files also, I mean signals will also be listed, provided you, get from that ucf file, once again which is not done here.

(Refer Slide Time: 28:12)

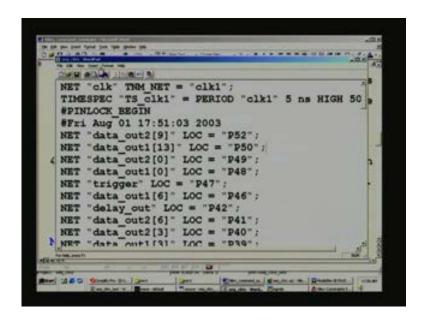

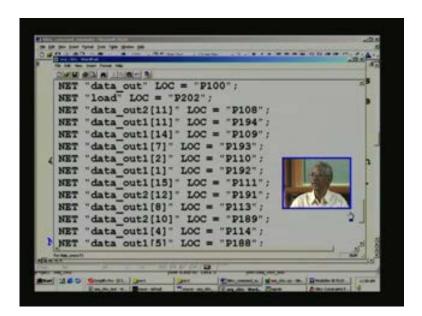

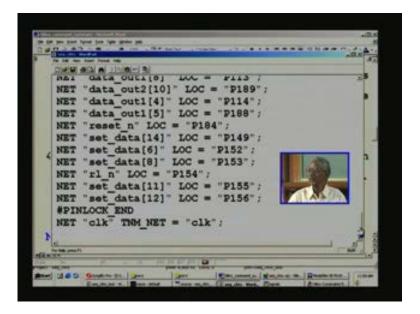

Now, I will show another ucf file after with all those pins, we have mapped earlier that is somewhere here. You can see final ucf file will look like this and you have the place and route itself has mapped it on to a particular pin all your signals, design signals and clock is here and then clock period, we have seen is 5 nano seconds here. You can even edit a file, ucf file. You can create your own file and on similar lines, and you can straight away run it right at the beginning. You could have given that dot ucf file at that point of time, then it would have taken all the pins, etcetera with your mapping; your choice will get affected.

(Refer Slide Time: 29:24)

| 200   | Constitution of the sub-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | and the local data data                      | .0.4                                     |       |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|------------------------------------------|-------|

| NE    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 100                                          |                                          |       |

| #2    | Partness                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Participant Income Party in                  | na Gereiter S                            |       |

| ØF    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | E .                                          |                                          |       |

| NE    | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1                                            | 1                                        | 3     |

| NE    | T intraspone later                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Bughan (                                     | etre.                                    | 8     |

| 4 NE  | Personal Streaments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Descriptions 1 and 1 and 1                   | ubes.                                    |       |

| NE    | and the second s |                                              | the Aut                                  |       |

| NE    | These Aust                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Alexand Har                                  |                                          |       |

| NE    | 10 10 10 10 - 10 10 10 10 10 10 10 10 10 10 10 10 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | a marticity.                                 |                                          | 1.22  |

| NE    | Net to the Just + 181                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                              |                                          |       |

| NE    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CONTRACTOR OF A DESCRIPTION OF A DESCRIPTION |                                          |       |

| NE    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Contrast Data State of Contrast              | C. C |       |

| D NTR | faile, pay fi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                              | - A.A.                                   | 비 제 집 |

So, otherwise, you can come from these constraints what we have just now seen. From there also we can change the pins as we have already seen, and I think we did not see the pins here, change, and that was constraints global ports, sorry. So, in ports, here, there is a pin here, say for example, let us say clock are b here. So, I can key in straight away there or I can just double click here. Another window opens. We can just key in there. I say this 239 here and say ok that gets reflected here.

So, whatever is entered here also appears here in the list. So, when, now, next step is to save this. Here, if you save, it will go into ucf file. The warning that it is giving is, after you have mind, you have made a major change here which is totally different from what it was earlier, all pin configuration, your, then clock, everything must have changed. So, all this will have to take effect totally.

So, in order to do this, you have to go back to prior to back annotation straight away to the implementation - place and route, xilinx place and route implementation - start from the implementation. Then, do the back annotation once again and then make sure the functionalities with the pins and that is how you have to go. So, that way that is time consuming thing and it is precisely the same that we have already followed. Therefore, that particular aspect will not be shown and it is enough if just see a ucf file. With that, I think you will be in a position to remap your I Os and as well as the clock.

(Refer Slide Time: 31:07)

| 1     | a bit for here tog                                                 |

|-------|--------------------------------------------------------------------|

| 1     |                                                                    |

|       | NET "clk" THM_NET = "clk1";                                        |

|       | TIMESPEC "TS_clk1" = PERIOD "clk1" 5 ns HIGH 50                    |

|       | #PINLOCK_BEGIN -                                                   |

|       | #Fri Aug 01 17:51:03 2003                                          |

|       | NET "data_out2[9]" LOC = "P52";                                    |

|       | NET "data out1[13]" LOC = "P50";                                   |

| 4     | NET "data out2[0]" LOC = "P49";                                    |

|       | NET "data out1[0]" LOC = "P48";                                    |

|       | NET "trigger" LOC = "P47":                                         |

|       | NET "data out1[6]" LOC = "P46";                                    |

|       | NET "delay out" LOC = "P42";                                       |

|       | NET "data out2[6]" LOC = "P41";                                    |

|       |                                                                    |

| R     | NET "data_out2[3]" LOC = "P40";<br>NET "data_out1[3]" LOC = "P39"; |

| -1    | NET ASTA ANTIINI INE B PIQT                                        |

| 64.00 |                                                                    |

(Refer Slide Time: 31:22)

(Refer Slide Time: 31:34)

We will first see the, this ucf file, we have already seen here. So, pin 52 for data out 2 signal and so on it goes. This has been created automatically during place and route, and as I mention earlier, during place and route, you can see the report browser and get various reports such as pad report or log report. All pad report will contains precisely this and here also you can have a look.

(Refer Slide Time: 31:42)

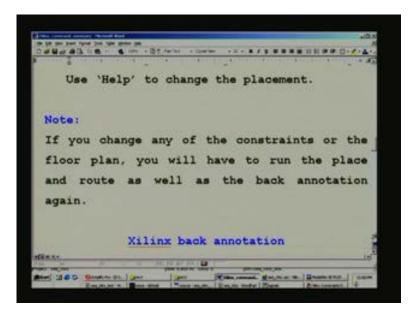

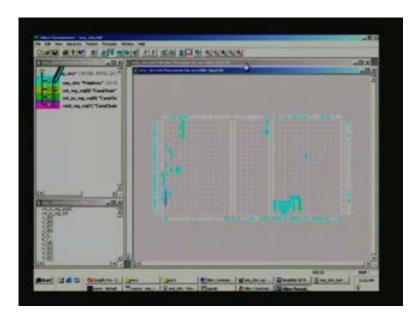

So, next what we will do is, I will go back to this comment here, and what we have here is floorplanner. Click on tools floorplanner to open the floor plan or layout of the design. So, this is the design which you can see as a layout, and use help to change the placement. This is involved, we will not go into depths of this and because it is quit involved, and right at the beginning stage, you do not really require, only towards the end of the project you actually require and help will take you step by step further.

(Refer Slide Time: 32:21)

So, we will see only very essentially things of the floorplanner. How it looks without going into too much details. One important notice, if you change any of the constraints or the floor plan, you will have to run the place and route as well as the back annotation again, that is what I mentioned here. So, you have to place and route once again implementation onwards, then go to back annotation and only then your new constraints such as pin or clock will take effect. We will now see the, so what it says here is, you have in under tools; you have a floorplanner here; just click on this.

(Refer Slide Time: 33:07)

(Refer Slide Time: 33:50)

| ACT AND A DESCRIPTION OF A DESCRIPTION O | 141                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| and a second second second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 24                                                                                                               |

| ric. a. all the family<br>ric. a. all the family<br>ric. all all the family                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | and the second |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                  |

| ž                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | the second second second                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                  |