### Switched Mode Power Conversion Prof. L. Umanand Department of Electronics System Engineering Indian Institute of Science Bangalore

### Lecture - 34 Controller and Sensing Circuit

Good day to all of you. We continue from where we left off in the last class. We were doing the controller design for dc-dc convertor from the model point of view. You remember that in an earlier class, we had done the controller design based on trial and error approach, and then we used the root locus technique where the small signal model of dc-dc convertor, that is the boost convertor was taken as an example, and then the root locus was plotted and on the root locus which gives basically the loci of the close loop pole location of the entire system along with the controller, a particular pole was chosen. It is responsible for the designer to choose a proper pole location and it is called pole placement, and using that value of gain corresponding to that chosen point on the root locus, the gain was substituted into the system controller and step response was seen and evaluated and then seen how close was to the performance specification. So, this iteration was continued till you reach a satisfactory design. So, this is the root locus process.

What we shall do today is, we use ngspice to simulate the circuit, boost convertor and the controller. We shall plug in the value which we obtain in the last class and see how it performs. During implementation and also simulation, you should keep one thing in mind that we are using the small signal model.

### (Refer Slide Time: 02:34)

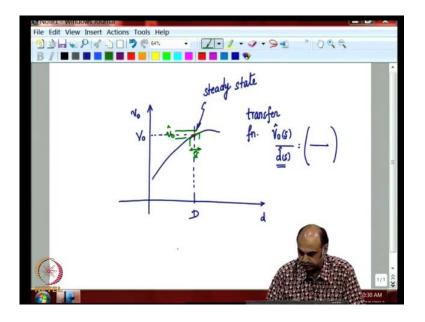

So, if we consider for example, the boost convertor, in the boost convertor, we had used the transfer function V naught S by d of s and they were all small signal model and you had some set of zeros and poles. Now, what those small signal variables indicate is that if you are having D verses V naught and as the D increases, let us say the V naught increases. At a given operating point D and V naught, uppercase D and uppercase V naught indicating steady state operating point. This is steady state.

So, in the neighbourhood of this steady state operating point, you have small deviation which is your d hat and v naught hat. So, the model actually is representing these small deviations in the neighbourhood of the operating point and therefore, that needs to be considered while implementing the controller design.

### (Refer Slide Time: 04:53)

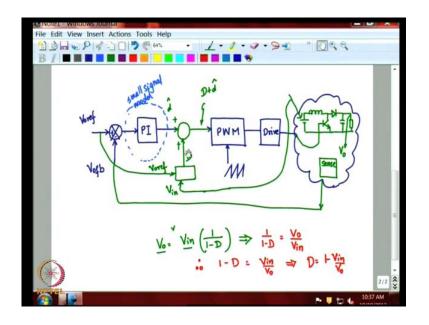

So, we make a slight modification even though this has been mentioned right at the beginning at the time of modelling. I will try to restate this problem and show. See normally our controller even in the trial and error approach, what we had was a comparator followed by a PI controller. Let us say a PI controller, we have V naught reference and we have V naught feedback. Now, the output of the controller goes to the pulse width modulator, PWM which actually has also another input triangle or a saw tool carrier determines the switching frequency and then, you have the driver which actually goes to the plant and the plant can be any convertor. In this case we had chosen a boost convertor like this. Let me indicate it in this fashion. So, the gate of it is actually controlled by this and you have V naught coming in there and this is feedback to this, of course there will be sensing circuitry to do that, to do the feedback portion.

Now, if you look at in the case of a switched mode convertor, what we have used to design in this controller is the small signal model. So, this portion should actually focus or should be the disturbance of the steady state operating point. So, in order to do that we introduce here a feed forward term like this plus and plus. Now, let us say this represents the voltage corresponding to D and this represent the voltage corresponding to D hat. So, what you would get here is the voltage corresponding to D plus D hat. The voltage corresponding to uppercase D or the steady state operating point is obtained from the steady state equation V naught is equal to Vin 1 by 1 minus D. Therefore, this is known, this is measured which is this point. This is also measured or the reference is known. We

could have what is the value. So, from here, we can have V naught by Vin equals 1 by 1 minus D and therefore, D 1 minus V equals Vin by V naught and D is 1 minus Vin by V naught.

So, what one can do is at this point have a calculator which takes in V naught ref, takes in Vin from here. This is V in V naught ref and calculate a voltage equivalent to D. So, this feed forward term ensures that even if this portion is not there, let us say it is 0. Under steady state, this will go to zero because the steady operating point is given by this term. So, this modification has to be done in all switched mode convertors, where you design the controller based on the small signal model of this because this is supposed to only handle small signal deviations in the neighbourhood of the steady operating point.

(Refer Slide Time: 12:21)

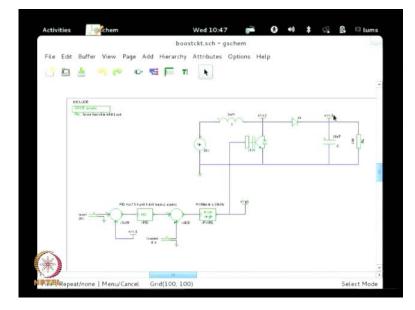

Now, I will try to show the boost convertor in spice. So, this is the gdea, gscan or the g schematic editor, where we normally enter the circuit and this is later on converted into a net list and ngspice is used for performing the simulation as we did in one of the previous classes for the buck convertor. So, let me zoom in on to the circuit.

So, this is the regular boost convertor. All of you are familiar with it by now. You have input dc voltage of 15 volts, you have the boost inductor; there is a power semiconductor switch, a diode and the capacitor followed by a load resistance. This node point is labelled as NVS and this is labelled as NVC. Now, this portion, this whole boost convertor is the plant. Now, the control input for the plant is the gate drive which is coming from the controller portion. So, if I zoom in the controller, you see that the control input what goes to the gate drive NVG is coming from the output of a PWM generator which is having a 20 kilohertz carrier, and what I was talking about just now is this portion.

See, you have a V naught reference is a 20 volt. You are feeding back in VC from the output node, comparator goes through a PID. This PID value is fixed to what we had found out the gain, what we found out from the root locus plot in the class. Remember that we had kept kp is equal to 0; kd is equal to 0 and found out ki as 7.5. You could include in the control structure 0 and then, later on try it as homework, try to found out the value of kp for different values and see how the response improves. Let as just try it out what we did in the last class.

Now, the output of the PID. Now, the PID was actually, the PI controller was actually designed using the small signals modules. So, these are small signal deviations in the neighbourhood of the operating point. So, let us say this is the steady operating point I am giving it from a source, constant source. You can actually put another calculation block here, sense the input voltage and the V naught ref here 1 minus V in by V naught will give you the D, and corresponding voltage at this point will give you the steady state D. These two are added which will give D plus D hat. The voltage corresponding to that go through PWM and gives the pulse here, pulse output with the duty cycle of D plus D hat will be given to the gate of the boost convertor power semi-conductors switch.

So, this is basically the modification that I was suggesting that we need to include, that is we need to have this feed forward term, such that the controllers operating for only this small signal term from in this steady state. In the steady state, this portion we had portion voltage corresponding D hat portion will become 0. So, here as I mentioned earlier in the other, we give actually the file name which contains the sub circuit models of all the components. Now, this particular circuit, let us now try simulate and see what would be the voltage at their output, this 20 voltage reference and we have a 15 volts which we want it to be boosted to 20 volts as we have referred here.

# (Refer Slide Time: 17:17)

| Activities                                                                                                                                                                        | Wed 10:48                                                                                       | 6         | 0   | 40) | * | 07 | ß    | 🗆 lums  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-----------|-----|-----|---|----|------|---------|

|                                                                                                                                                                                   |                                                                                                 | NUMP.     |     |     |   |    |      |         |

| lums@loca                                                                                                                                                                         | alhost:"/lums_dir/NPTEL/I                                                                       | boost_clo | ose |     |   |    |      |         |

| File Edit View Search Terminal                                                                                                                                                    | Help<br>List<br>Joy SDB<br>Lsting capability.<br>prorson.com/gEDA/SPI0<br>etlist of main design | ж.<br>ж.  |     |     |   |    |      |         |

| L 3 075 JRH<br>VIN 3 0 15V<br>D NVs NVC Def<br>C NVC 0 10P<br>FWM1 2 NVg PWMtri fs = 20kHz<br>.NDCLUDE /home/lums/bin/edt01.s<br>Voref 1 0 20V<br>.end<br>FSS any key to continue |                                                                                                 |           |     |     |   |    |      |         |

| Repeat/none   Menu/Cancel Gr                                                                                                                                                      | rid(100, 100)                                                                                   |           |     |     |   |    | Sele | ct Mode |

## (Refer Slide Time: 17:54)

| Activities            | Terminal                                                              | Wed 10:48                | 6          | •       | <b>\$</b> | 1 B    | 🖾 lums    |

|-----------------------|-----------------------------------------------------------------------|--------------------------|------------|---------|-----------|--------|-----------|

| 2                     |                                                                       |                          |            |         |           |        | _         |

|                       | lums@loca                                                             | lhost:"/lums_dir/NPTEL/E | oost_close |         |           |        | 1         |

|                       | View Search Terminal H<br>T to USE A PREVIOUSLY                       |                          | 2          |         |           |        |           |

| [ 1] No<br>[ 2] Yes   |                                                                       |                          |            |         |           |        | -         |

| pick a num            | ber, any number: l                                                    |                          |            |         |           |        |           |

|                       | circuit definition f<br>use existing .cir fil                         |                          | new .ci    | file [  | 1/0] =    | I      | C.e.      |

| • .option<br>.tran lu | on of boostckt.cir<br>reltol=0.81 abstol=0.<br>10m uic<br>oostckt.net | 001 vntol=0.091          |            |         |           |        |           |

|                       | ny key to simulate -<br>ce shell                                      | after simulation typ     | e "exit"   | or "qui | t' to c   | ome ou |           |

|                       |                                                                       |                          |            |         |           |        |           |

|                       |                                                                       |                          |            |         |           |        |           |

| 2                     |                                                                       | - M                      |            |         |           |        |           |

| Pit Repeat            | t/none   Menu/Cancel Gri                                              | d(100, 100)              |            |         |           | Se     | lect Mode |

### (Refer Slide Time: 18:03)

| Activities - Terminal               | Wed 10:48            | 0          | 0 | Ŧ | 92 | 🔒 🗆 lums    |

|-------------------------------------|----------------------|------------|---|---|----|-------------|

|                                     |                      |            |   |   |    |             |

| lums@localhost                      | t:~/lums_dir/NPTEL/I | boost_clos | e |   |    | 1.0         |

| File Edit View Search Terminal Help |                      |            |   |   |    |             |

| xpid.ni                             | 0                    |            |   |   |    |             |

| xpid.nd                             | 0                    |            |   |   |    | <u>^</u>    |

| xpid.nvsum                          | 0                    |            |   |   |    |             |

| nvs                                 | Θ                    |            |   |   |    |             |

| xsw.ndb                             | 0                    |            |   |   |    |             |

| nva                                 | 0                    |            |   |   |    |             |

| 3                                   | 0                    |            |   |   |    |             |

| xpwml.nptri                         | Θ                    |            |   |   |    | h.          |

| xpwml.ncout                         | 0                    |            |   |   |    | 1           |

| l#branch                            | .0                   |            |   |   |    | T.          |

| voref#branch                        | Θ                    |            |   |   |    |             |

| vin#branch                          | 0                    |            |   |   |    | ľ           |

| vcontrol#branch                     | Θ                    |            |   |   |    |             |

| a.xpid.adif#branch 1_0              | Θ                    |            |   |   |    |             |

| a.xpid.aint#branch 1 0              | 0                    |            |   |   |    |             |

| a.xpwml.alim#branch_1_0             | 0                    |            |   |   |    |             |

| a,xpid.apidlimit#branch_1_8         | Θ                    |            |   |   |    |             |

| a.xpwml.acompare#branch_1_8         | Θ                    |            |   |   |    |             |

| a.xpid.asig@a#branch_1_0            | 0                    |            |   |   |    |             |

| a.xsum.asum#branch_l_0              | Θ                    |            |   |   |    | 1           |

| a.xadd.asum#branch_1_0              | Θ                    |            |   |   |    |             |

| a.xpwml.atri#branch_1_0             | 0                    |            |   |   |    |             |

|                                     |                      |            |   |   |    |             |

| ence value : 4.93008e-04            |                      |            |   |   |    |             |

|                                     | N.                   |            |   |   |    | )           |

| Repeat/none   Menu/Cancel Grid(10   | 0, 100)              |            |   |   |    | Select Mode |

### (Refer Slide Time: 18:15)

| Activities * Terminal                  | Wed 10:49                    | <b>1</b>   | Ø | <b>4</b> 0) | * | r. E | i 🗆 lu  | ms  |

|----------------------------------------|------------------------------|------------|---|-------------|---|------|---------|-----|

|                                        |                              |            |   |             |   |      |         |     |

| lumsi                                  | @localhost:~/lums_dir/NPTEL/ | boost_clos | e |             |   |      | -       |     |

| File Edit View Search Termi            | nal Help                     |            |   |             |   |      |         |     |

| <pre>10. v(xpid.nvsum)</pre>           |                              |            |   |             |   |      |         |     |

| 11. v(nvs)                             |                              |            |   |             |   |      |         | -   |

| 12. v(xsw.ndb)                         |                              |            |   |             |   |      |         |     |

| 13. v(nvg)                             |                              |            |   |             |   |      |         |     |

| 14. v(3)                               |                              |            |   |             |   |      |         |     |

| 15. v(xpwnl.nptrl)                     |                              |            |   |             |   |      | h       |     |

| <pre>16. v(xpwml.ncout) 17. i(l)</pre> |                              |            |   |             |   |      |         |     |

| 17. 1(t)<br>18. 1(voref)               |                              |            |   |             |   |      | 1       |     |

| 19. 1(vin)                             |                              |            |   |             |   |      |         |     |

| 20. 1(vcontrol)                        |                              |            |   |             |   |      |         |     |

| 21. 1(a.xpid.adif)                     |                              |            |   |             |   |      | 1       |     |

| 22, i(a.xpid.aint)                     |                              |            |   |             |   |      |         | 1   |

| <pre>23. i(a.xpwml.alim)</pre>         |                              |            |   |             |   |      |         |     |

| <pre>24. i(a.xpid.apidlimit)</pre>     |                              |            |   |             |   |      |         |     |

| <pre>25. 1(a.xpwml.acompare)</pre>     |                              |            |   |             |   |      |         |     |

| 26. i(a.xpid.asigma)                   |                              |            |   |             |   |      |         |     |

| 27. 1(a.xsum.asum)                     |                              |            |   |             |   |      |         |     |

| 28. 1(a,xadd.asum)                     |                              |            |   |             |   |      |         |     |

| 29. i(a.xpwml.atri)                    |                              |            |   |             |   |      |         |     |

| TO QUIT: enter x-axis = 0              |                              |            |   |             |   |      | 1       |     |

| alex-axis number (press                | ENTER for 'time' as defa     | ult):      |   |             |   |      |         |     |

| 9                                      | 14                           |            |   |             |   |      | -       | >   |

| Repeat/none   Menu/Cancel              | Grid(100, 100)               |            |   |             |   | 0    | elect M | ode |

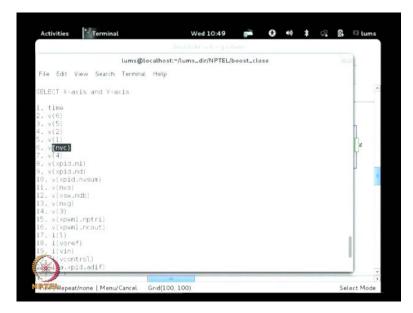

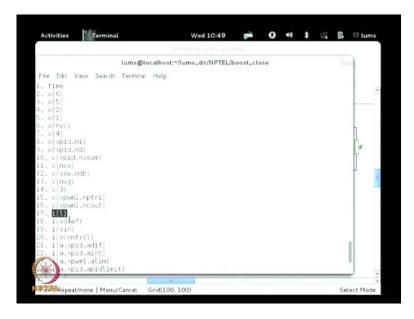

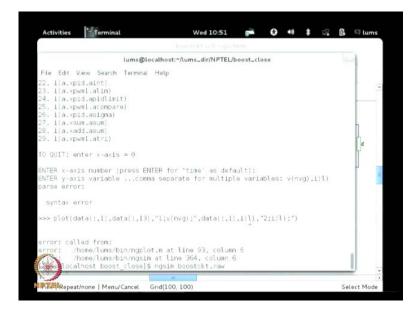

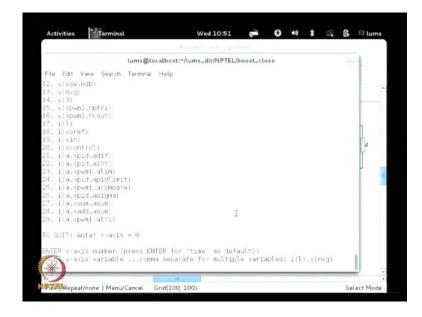

So, going back to the command line let me go to that particular folder. Now, I will run ng spice through a script file written in octave called ngsim boost circuit dot schematic. So, when you run that, the first thing that will be done is the net list will be generated and later, we go into the ngspice simulator engine which does perform the simulation, calculates all the node voltages in the branch current and gives you all the possible variables which can be observed. You see that here NVC, the node which we are labelled as the output, you want to see that.

### (Refer Slide Time: 18:24)

### (Refer Slide Time: 18:34)

| Activities                     | 2      | Termina  |          |           | Wed 10:49        | 6         | •   | 40) | * | 02 | e.  | 🖾 lums    |

|--------------------------------|--------|----------|----------|-----------|------------------|-----------|-----|-----|---|----|-----|-----------|

| 23                             |        |          |          | 6         | ice- (a) Gran    | ALC: NO.  |     |     |   |    |     |           |

|                                |        |          | lums@lo  | calhost:" | /lums_dir/NPTEL/ | boost_clo | ose |     |   |    |     |           |

| File Edit                      | View   | Search   | Terminal | Help      |                  |           |     |     |   |    |     |           |

| 1. time                        |        |          |          |           |                  |           |     |     |   |    |     | -         |

| 2. v(6)                        |        |          |          |           |                  |           |     |     |   |    |     |           |

| 3. v(5)<br>4. v(2)             |        |          |          |           |                  |           |     |     |   |    |     |           |

| 5. v(1)                        |        |          |          |           |                  |           |     |     |   |    |     |           |

| 6. v(nvc)                      |        |          |          |           |                  |           |     |     |   |    |     |           |

| 7. v(4)                        |        |          |          |           |                  |           |     |     |   |    |     |           |

| 8. v(xpid                      |        |          |          |           |                  |           |     |     |   |    |     | R.        |

| <pre>9. v(xpid 10. v(xpi</pre> |        | 1001     |          |           |                  |           |     |     |   |    |     | L.        |

| II. v(nvs                      |        |          |          |           |                  |           |     |     |   |    |     |           |

| 12. v(xsw                      |        |          |          |           |                  |           |     |     |   |    |     | F         |

| 13. @(nvg                      | 1      |          |          |           |                  |           |     |     |   |    |     |           |

| 14. v(3)<br>15. v(xpw          | n) nn  | t eff.   |          |           |                  |           |     |     |   |    |     |           |

| 16. v(xpw                      |        |          |          |           |                  |           |     |     |   |    |     |           |

| 17.1(1)                        |        |          |          |           |                  |           |     |     |   |    |     |           |

| 18. 1(vor                      |        |          |          |           |                  |           |     |     |   |    |     |           |

| 19. 1(vin<br>20. 1(vco         | ()     |          |          |           |                  |           |     |     |   |    |     |           |

| 20, 1(vco<br>21, 1(a.×         |        |          |          |           |                  |           |     |     |   |    |     |           |

| 22. i(a.x                      |        |          |          |           |                  |           |     |     |   |    |     |           |

|                                | pwml.  |          |          |           |                  |           |     |     |   |    |     |           |

| 28 4 a.×                       | pid.a  | pidlimi  | t)       |           |                  |           |     |     |   |    |     |           |

| 1 and                          |        |          |          |           |                  |           |     |     |   |    |     | >         |

| Pit ARepe                      | at/non | e   Menu | Cancel   | Grid(100, | 100)             |           |     |     |   |    | Sel | lect Mode |

### (Refer Slide Time: 08:47)

We could see NVG; the one which we want is basically the pulse width modulated wave form, the pulses which are given to the gate. We could see that. We could also see the (( )) current through the inductor. So, one by one we could have a look at how these look like, so if you see the voltage of NVC and the voltage V naught ref.

(Refer Slide Time: 17:17)

| Activities Terminal                                | Wed 10:48                               | 6        | Θ  | 40) | * | <u>0</u> 2 | ß    | 🖾 lum   | 5  |

|----------------------------------------------------|-----------------------------------------|----------|----|-----|---|------------|------|---------|----|

|                                                    |                                         |          |    |     |   |            |      |         |    |

| lums@local                                         | lhost:"/lums_dir/NPTEL/b                | oost_clo | se |     |   |            |      | 1       |    |

| File Edit View Search Terminal H                   | elp                                     |          |    |     |   |            |      |         |    |

|                                                    |                                         | *****    |    |     |   |            |      | F       |    |

| <ul> <li>Spice file generated by gnetl.</li> </ul> | ist                                     |          |    |     |   |            |      |         | ^  |

| * spice-sdb version 4.28.2807 b                    | y SDB                                   |          |    |     |   |            |      |         |    |

| * provides advanced spice netlight                 | sting capability.                       |          |    |     |   |            |      |         |    |

| * Documentation at http://www.b                    | rorson.com/gEDA/SPIC                    | E/ +     |    |     |   |            |      |         |    |

| * * * * * * * * * * * * * * * * * * * *            | * * * * * * * * * * * * * * * * * * * * | *****    |    |     |   |            |      | L       |    |

| · Begin SPICE ne                                   | tlist of main design                    |          |    | 100 |   |            |      |         |    |

| Vcontrol 6 0 -0.4                                  |                                         |          |    |     |   |            |      | h.      |    |

| xADD 5 6 2 add                                     |                                         |          |    |     |   |            |      | 14      |    |

| xSUM 1 nVc 4 sum                                   |                                         |          |    |     |   |            |      | Tr .    |    |

| xPID 4 5 PID K1=7.5 Kp=0 Kd=0 1                    | sat=-1 usat=1                           |          |    |     |   |            |      |         |    |

| xSW nVs 8 nVa power sw                             |                                         |          |    |     |   |            |      | ۲       |    |

| RL O nVc 1)00                                      |                                         |          |    |     |   |            |      |         |    |

| L 3 nVs 2mH                                        |                                         |          |    |     |   |            |      |         |    |

| Vin 3 0 15V                                        |                                         |          |    |     |   |            |      |         |    |

| D nVs nVc Def                                      |                                         |          |    |     |   |            | _    |         |    |

| C nVc 0 10uF                                       |                                         |          |    |     |   |            | _    |         |    |

| xPwM1 2 nVg PwMtri fs = 20kHz                      |                                         |          |    |     |   |            |      |         |    |

| .INCLUDE /home/lums/bin/edt01.st                   | ub                                      |          |    |     |   |            |      |         |    |

| Voref 1 8 20V                                      |                                         |          |    |     |   |            |      |         |    |

| .end                                               |                                         |          |    |     |   |            |      |         |    |

|                                                    |                                         |          |    |     |   |            |      |         |    |

| PRESS any key to continue                          |                                         |          |    |     |   |            |      |         |    |

| *                                                  |                                         |          |    |     |   |            |      |         | -  |

|                                                    | 10                                      |          |    |     |   |            |      | -       | 5  |

| PTRepeat/none   Menu/Cancel Gri                    | d(100, 100)                             |          |    |     |   |            | 4.11 | ect Mod | 20 |

### (Refer Slide Time: 19:47)

(Refer Slide Time: 20:11)

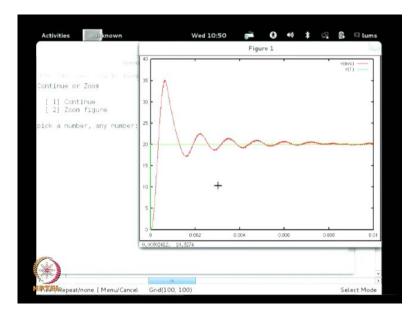

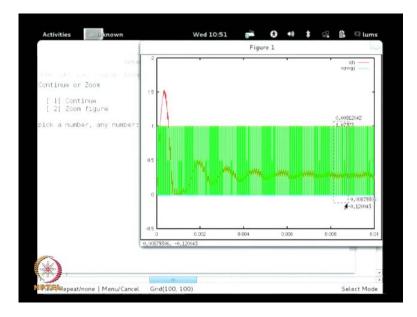

Now, if you look at the net list here, V naught ref is node 1. So, we could see node 1 also, V of node 1. So, you see that this is the green waveform is node 1 which is actually the reference and the output voltage is trying to get controlled and reaches the stable state. You could zoom in and try to see the nature of the ripple, calculate and study all those characteristics.

### (Refer Slide Time: 20:43)

(Refer Slide Time: 20:49)

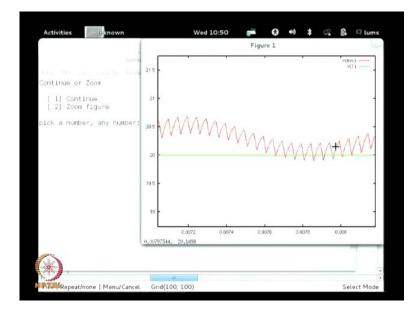

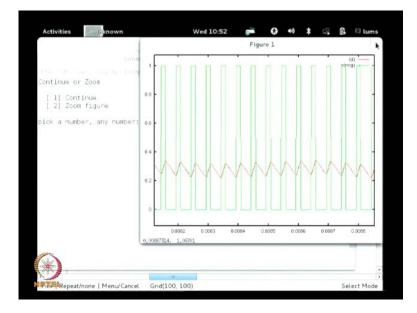

We could also have a quick look at the il waveform and nvg waveform. The inductor current waveform and you see, these two super posts, let us zoom in so that we could, so let me zoom near the steady state portions.

### (Refer Slide Time: 21:02)

### (Refer Slide Time: 21:13)

So, this is the red waveform is the inductor current waveform, and the green waveform is actually the pulse width modulated waveform that has been generated to achieve that steady output voltage of 20 volts. So, this pulse width modulated waveform 0 to 1 is actually the gate drive signal which is given to the boost convertor switch and you see this triangular waveform in the current waveform in the inductor as discussed in the analysis of the boost convertor, ok.

### (Refer Slide Time: 21:59)

(Refer Slide Time: 22:16)

| a noter windows tounion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | and have been seen as |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| File Edit View Insert Actions Tools Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                       |

| SOUCH STORE - Z. · 2 · 2 · 2 · 2 · 2 · 2 · 2 · 2 · 2 ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                       |

| () - Trial & Error<br>(Ziegler-Nichols<br>method)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                       |

| 2. Model based                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                       |

| ton ROOT LOCUS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                       |

| <ol> <li>Model based</li> <li>Model based</li> <li>Hno' ROOT LOCUS</li> <li>Technique</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3/3                   |

| NUMER OF THE OWNER OWNE | ×                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 50 450 AM             |

So, we stop here at this point and let me go over back to the white board. So, we have discussed the trial and error approach something similar to Ziegler-Nichols method, and we have seen the other model based through the root locus technique. As I said people have used bode plot technique that also is quite popular using the gain and the phase margin. However, for the switch mode power convertors, where they are made using the three primary convertors, the building blocks like the boost convertor, the buck convertor, the buck boost convertor. The boost convertor in particular has 0 on the right of the s plane, bode plot is not valid and cannot be used for such non-minimum phase

system and all the boost derivatives will not be in a position to be addressed by bode plot method.

The root locus method is much more general approach and it is something similar to the pole placement approach of the state space, or the model control systems and this can be applied even for non minimum pace systems. Therefore, the root locus technique can be used when you know the model of the system well, and when you have the small signal model or even the large signal model and if the system is a black box, apply the trial and error method.

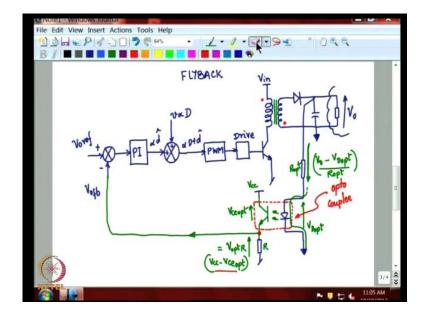

Now, let us go forward and see some of the problems that we would get during implementation. Now, let us take the example of an isolated convertor. Now, isolated convertor or the forward convertor, the half bridge, push pull and the fly back convertor. Let us take the one of the popular topology like the fly back convertor, and see how the feedback is achieved. You remember that we were discussing while feeding back, we just drew a line from the outputs to the feedback point, but actually there is a sense circuit in between and let us have a look at that sense circuit, so that we have a complete schematic.

(Refer Slide Time: 25:37)

So, if we take the fly back convertor, it is of this form. You have the fly back transformer which is also actually an inductor, where I am using this b j t or i j b t. You can actually replace it with mosfet, i j b t or b j t or let say, you have this drive and this comes from

the output of the PWM signal in this fashion. Now, on the secondary side, we have just a diode and capacitance which goes on further to other loads. Let me indicate it as a resistive load in this fashion. It is very important to note that the dot polarities of the transformer are in this fashion for the fly back as you have studied earlier in the class.

So, briefly the operation is very simple when the switch q is on. You have dot as positive at Vin, and the non dot end as connected to the ground that is 0. Therefore, this dot end is positive, this dot end would also be positive. In the secondary side reverse places the diode and the diode is off, the secondary side portion is off. Only the capacitance is discharging to the load. So, during this time the current flow through this transformer, this is actually an inductor. It has a near gap inside and starts storing energy in the reluctance within the (()). When this is switched off, the energy which is stored within is now released, starts freewheeling through secondary. There is a reversal of polarity, the non dot end becomes positive, this becomes positive, and this will try to forward bias the diode and pump the energy into the capacitance, and there by replenish the charge that the capacitance lost during the cycle when this diode was off.

So, this is briefly how it operates. This is the fly back convertor and here, we have the comparator, compare and control plus minus, you have V naught reference and V naught feedback, the output of which goes into the controller, PI controller which is plus and plus. So, you give a voltage which is proportional to D here and this voltage is proportional to D hat, and this will be proportional to D plus D hat.

Now, all along we have been trying to say that this of course is V naught. You take V naught and feed it back here, every simple line. However, in practice we cannot just draw a simple line such like that. There are two issues. One is compatibility and another is there is this isolation. This main function of the transformer, one of the main function of the transformer is to achieve a voltage scaling, such that the load voltage becomes compatible with a Vin for a given duty cycle, and the other function is input and output galvanic isolation. That is also a very key important parameter to be addressed because most of the time, you like to have isolation of the load with the input side power and also with the control side power. Therefore, we need to interpose in between here something which does maintain that isolation, and also sends across the information.

So, one of the very nice way do that is to use an opto coupler and like this, I will use a different common point symbol. Observe that these two labels or symbols are connected and this is different. These are galvanically separated. They are not connected together. So, it is like saying that we have a thick line wire connecting these two, but in order not mess up the paper, we normally keep this line out and then, put a symbol at this point and the same symbol at this point indicating that these two are wired tightly together. So, the opto coupler is having the diode on the primary side and has b j t on the secondary side and together, it is available as a pack in this form. So, this is the opto coupler.

Now, considering this kind of opto coupler connected in this fashion, we shall introduce one more component here instead of connecting the voltage directly through to the opto coupler, we normally would like to protect it, allow only predefined amount of current to flow through. So, you need to have a resistance and allow only that much amount of opto current for which it is rated and then, let us say we have a resistor here and then, you have some voltage which is connected across that with respective to ground. Now, if you tap at this point and draw the signal from here, this signal we will call at this one V opt across R. This signal will be a measure of the output V naught. Consider the current which flow through like this through this R opt. So, it will be V naught minus. If this is V D opt divided by R opt will be the current that is flowing through in this resistance through the primary into this virtual grounded output which actually comes back here complete the circuit. So, this is how it would be going.

Now, this amount of current comes and flows through. This will bias this transistor, the opt transistor here and it will be at some operating point, and it will have some V ce. So, what appears across here would be if this is V cc minus V ce opto, this is V ce opto, so the voltage across the emitter resistance r, is this value. So, as the voltage V naught increases, I increases, the transistor is biased more to the saturation, V ce opt decreases and once this decreases, V cc minus V ce opt increases or V opt across R increases. So, this value increases. So, v naught increases, this value increases. V naught decreases, the current through decreases. The transistor is bias more away from the saturation V ce op t increases and V opt decreases because of this.

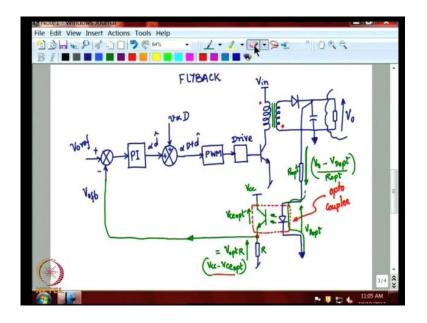

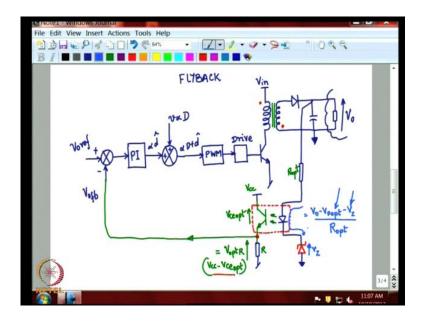

### (Refer Slide Time: 25:37)

So, this point tries to have the same proportionality with respect to V naught and also, preserving the galvanic isolation. So, this V c connected here in more size in circuits, where you need size output regulation, the transfer ratio, the current transfer ratio, the opto coupler, and the voltage across the opto coupler is dependent on a temperature, especially the voltage V D of is dependent on temperature. As temperature varies, this value varies and therefore, current varies and therefore, the bias point varies. Therefore, the output that is feedback here even if the voltage here, V naught has not vary. Because of the temperature variation, this value would have varied and the controller thinks that the output is varied and tries set two different values. Therefore, in order to compensate of the temperature, normally another component is included.

### (Refer Slide Time: 40:07)

So, before that let us clean up some of these things here. Yes and this. So, here the new component that I am going to add is a senor and then, you are connected to. Now, choose senor such that these two are having an opposite temperature coefficient. So, this is having a positive temperature co efficient and this should have negative temperature co efficient, so that there is compensation.

Now, the current that flows through this opto would be equal to V naught minus V D opt minus V Z. This is V Z divided by R opt output. So, if there is a temperature change and if this has the positive temperature coefficient and there is an increase in a negative temperature coefficient, if that decreases and this is the positive temperature coefficient, there will be increase and then, that would try to compensate each other. So, this is normally put in high position regulators in order to compensate for the temperature.

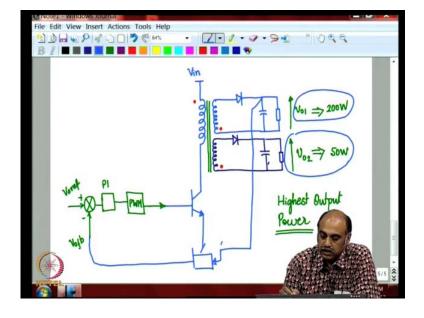

So, this is how one would sense the output voltage and pass it on to the controller. Now, the next issue that is of vary is normally in isolated converter just like fly back converter that we saw. You do not have just one single output, there are multiple outputs. There may be a 5 volt output; there may be a 15 volt output, minus 15 volt output and so on. 3.3 output volt that have many output generally could have 3 to 5 outputs and you have just one control input. There is only one transistor, one b j t or mosfet, the gate of which can be controlled. Therefore, only one value of duty cycle can be applied to the power

semiconductor switch. However, you have multiple outputs, multiple loads. What do we do in such case? So, let us take an example.

(Refer Slide Time: 43:07)

For that again I am going to draw the fly back converter. So, consider this fly back converter that I am drawing here and secondary is like this. So, if this is Vin, do not forget the dot polarity fly back converter has dot polarity and what about the multiple outputs. What do we do or how does it appear? We could have, let us say another output in this fashion and that is also covered to the same core. All three windings are placed same in core, the primary, secondary one and secondary two. So, this is just an example with two outputs, but there could be many more number of outputs. So, let us say this is V naught 1 and this is V naught 2. So, you have two outputs and there is only one control input which of course goes through the drive. You have all these controllers and I am going to just put briefly block PWM drive. So, all of this coming in near with V naught reference which V naught reference would you, which is the V naught reference that has to fed back from the output side, what would be fed back here and what should be V naught reference here? This is one of the questions.

So, with one control input, you can control only either this or this. So, normally we take that particular output which is having the highest output power. That output which has the highest output power is the one which would be fed back. So, if you say that V naught 1 is going to feed a maximum output power of 200 watts and V naught 2 is going

to feed 50 watts max, then this is the output that will be fed back and take that, pass it through the opto circuit and feed that back.

File Edit View Insert Actions Tools Help Pie Edit View Insert Actions Tools Help Other un controlled outputs NEED to be locally regulated How? 1. Linear Regulate 2. Switched non-isolated topology 3. Coupled inductor 4. Magnetic amplifier mettrod.

(Refer Slide Time: 47:49)

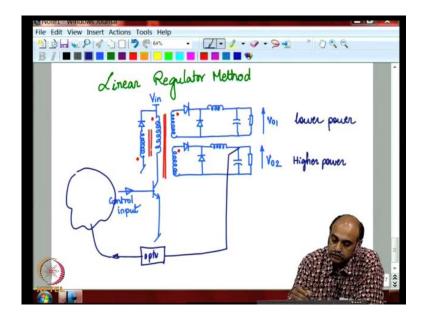

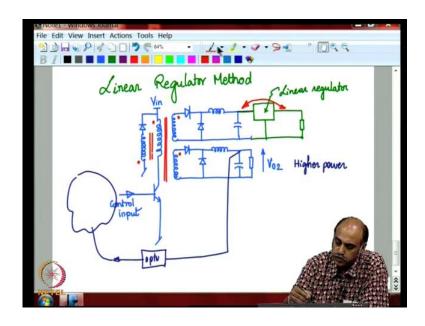

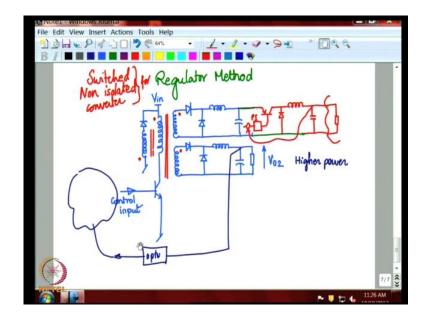

What happens to V naught 2? What happens to the other output or other outputs? There are more than 2. They need to be locally regulated. The other uncontrolled outputs need to be locally regulated. How? There are few methods and one method is linear regulator method using switched non isolated topology. You could use coupled inductor method. There is the magnetic amplifier method. These are some of the more popular ways by which regulation of the uncontrolled outputs are addressed. So, we shall see these possibilities because in a practical power supply, you will always find power supplies having multiple outputs. So, one by one let us take up these methods and see how it is accomplished.

(Refer Slide Time: 50:04)

So, first by the linear regular method. It is very simple. Let me draw this time, I will draw another converter instead of fly back. Let me draw the forward converter with demagnetizing winding. It could be half bridge, full bridge, fly back, any just that to break the monotony, I will try to draw some other converter. This is the topology of the forward converter isolated multiple outputs. It is not very popular though because of too many inductor components. I will just draw two outputs. These are the two outputs. You have the load across them and this is the control input.

Dot polarities in the forward case, the dot polarities are like that. Refer back to your class and be careful. The dot polarity of this is the opposite. All are on the same core, and this is Vin, this is v naught 1, v naught 2. So, what is the operation? When the switch is on, this primary winding is connected to ground, the dot portion is Vin and by the terms ratio times, the dot here is positive, dot here is positive, turns on this diode, the forward biases and the potential occurs across this diode. This diode is reverse biased, charges up the inductor and capacitance in the inductor is building up, the inductor energy is also building up.

Now, because this dot is positive, this diode is reversed biased. Now, this is switched off. The moment this is switched off, there is the reverse law polarity, dot end becomes negative, non dot becomes negative, non dot becomes positive here, non dot is positive. This diode is turned off; the inductor will start freely like this at the same time because non dot end is positive, this is positive. This will turn on diode and put energy into the supply. So, the magnetizing energy is pushed into the supply. So, this is the operation of forward converter which we already know.

Now, the problem as I was trying to tell is how we control the two outputs. So, depending upon the power; now let us say that this is the higher power, this is the lower power one. So, higher power let as feedback through our regular opto circuit that we discussed to the control version.

(Refer Slide Time: 55:12)

Now, for the lower power let us do a local regulation with a linear regulator. If it is a linear regulator, three pin fixed linear regulator and then, give it to the load. So, this would be a linear regulator, three pin regulator, either a fixed one like this. 1 7 8 series are the variables ones at the 3 1 7, those type of regulator. So, what happen is that the pulse with modulated switching converter here tries to bring the voltage here to a more compatible voltage to the output. It is only different by the amount of regulation and this block. So, this block is this probe here across the linear regulator is maintained to just a minimum, so that the loss is kept minimum and further, this is a low power side. So, this linear regulator does the job of regulating this unregulated portion and thereby providing a good regulated output here. The higher power output portion is automatically getting regulated because that voltage is fed back through the opto given to the controller which gives the proper controller signal to modulate the drive duty cycle here.

(Refer Slide Time: 57:31)

So, on adjusting the duty cycle here, not does this only change, this would also change that the variation here is regulated by this linear regulated. Instead of using a linear regulator, one could use a switched mode regulator point. The regular bulk converter says you could have a buck converter like this, another small inductor, capacitance and the load and you have a small PWM and the local control, and this is feedback here, the voltage. So, this would be a v i p wm, this would be a local regulator based on T 1 4 9 4 or any other pulse with modulator which is using the output voltage here itself power supply to power up all these portions control circuitry. This portion, the control circuitry is powered up by this or powered up by the regulated unregulated voltage of this at this point. Then, the gate drive is supplied to transistor which does the buck operation here and then, appropriately you get a regulator voltage at this point.

So, this is a local regulation and such type of locally regulated converters is basically called switched non isolated converters for regulating the output. So, this is the second method. That means first method linear regulator where this portion was replaced with linear regulator, so that it is the output regulator. Instead of linear regulator, you can use a switched non-isolated topology like the buck, the boost buck depending upon the output that would like to regulate here and use that output voltage for having a local feedback control loop which will adjust the duty cycle of the switch here, and give a regulated output. The other winding, output winding goes through the same way as we have discussed now. Now, there are two other methods, coupled inductor method and the

method of magnetic amplifier which we will have to discuss which we shall do in the next class.

Thank you.