## Power Management Integrated Circuits Dr. Qadeer Ahmad Khan Department of Electrical Engineering Indian Institute of Technology, Madras

## Lecture – 86 Introduction to Switched-Capacitor DC-DC Converters, Switched-Capacitor DC-DC Converter with V0=2\*VDD

(Refer Slide Time: 00:14)

| Lances prove area arrest                            | (              |

|-----------------------------------------------------|----------------|

| suitched Capacitor DC-DC converter                  | NP             |

|                                                     |                |

| switched capacitor is used as senistor              |                |

| Via J Vo =Vad                                       |                |

| $V_{Ld} = V_{dc} = V_{dc} = V_{dc} = \frac{1}{6vc}$ |                |

| por Te s minu                                       |                |

| / Ť4                                                |                |

| Plying cyciton stringe (order)                      |                |

| Thying cyneitar strenge (anger)<br>Cafastar         |                |

| yauto.                                              |                |

| Vo = 2xVda                                          |                |

| 10 - allinge                                        |                |

| . E F                                               |                |

| Var I Vo Daving & Vallage in Cp                     | 3 23           |

| F They Ver = Vad                                    |                |

| First usy = var                                     | and the second |

| P _ F = FF            |                |

|                                                     |                |

|                                                     |                |

So, usually in a standard analogue circuit, your switch capacitor is used as what? Resistor ok, but here in the switched capacitor DC-DC converter, we are basically delivering power to the output. So, we use it as a charge carrier. In the other case also; it is a charge carrier, but it behaves like a resistor. Here also each stage will behave like a resistor, but the requirement for that resistor is very small because, if you keep a very high resistor then we know that losses will be high.

So, the difference in a standard switch capacitor circuit and DC-DC converter is that the power requirements are different ok. Just like if you have, we were talking about the LC filter. So, in the LC filter path, you cannot basically afford to have a large resistor, the conduction losses will be high.

But now, the same filter, let us say you are designing for any analogue signal processing, I want a low pass filter. You do not have as such any current requirement there. So, you can build with a very large R and a small c. So, that is the main difference between the two. So, if let us say I have this V dd this is my switch this is C 1 this is C 2 if this is phi and this is phi bar, they are non-overlapped complimentary phases.

So, if this is V out, what will be V out after infinite cycles? It will be V dd. Every cycle you are you are taking the charge from V dd and dumping on the output. If you keep doing the for like infinite cycles, ultimately your output has to go to V dd. You do your charge sharing every cycle; you will see your output will keep increasing ok. Even though the disturbance will get smaller.

So, the first time you do let us say V out is 0, then you will see the jump will be large. Then after that a smaller jump because of the charge sharing. So, this is nothing, but same thing and you will see your relationship will be looking similar like exponential because the step size is getting smaller and that is what happens? When your output is charged near V dd, it gets slower it slows down. So, the same thing happens here also and this R is 1 over what ok.

So, which means, if I want to reduce R, what do I need to do? Increase the switching frequency or increase the capacitor. So, if I want to deliver I mean. So, if I am building a normal rc filter and I do not have any load requirement then Fsw and C required may not be that large, but now if I put a load at V out then what would happen? So, there is no load. Now the moment I put a load what will happen?

V out will start dropping, which means; you have to charge the output much faster or your capacitor should have more charge stored in it. So, that is why you have two options, either you basically fill the output much faster or increase the size of your capacitor. So, this is flying cap. So, this is and this guy is storage. You can call it output capacitor also.

So, in this case V out equal to V dd, but when we want to regulate the output we do not want it usually. We do not want that there, we can just short V out and V dd, but this just. So, now, if I rearrange the switches everything so that, if I want let us say, V out equal to V dd by 2.

So, you have to rearrange these switches in such a way that you can get V dd by 2 and there is an analogy also.

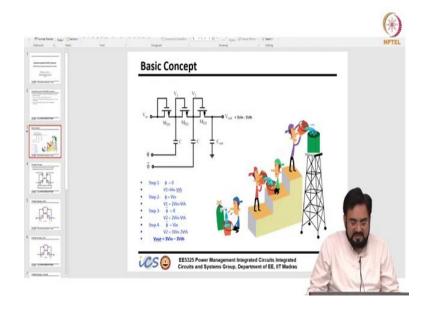

(Refer Slide Time: 06:10)

So, you can think about this is your output cap bucket big bucket and these guys are switches actually they are carriers and this smaller capacitor here is the flying capacitor.

So, you have a source. So, this is your V dd and you fill the bucket and you transfer to the next. So, here I have shown only one stage now, if let us say I have one more stage ok. Usually depending upon what ratio you require between output and input your number of stages may be different.

So, here it is a boost converter it is a 3 x actually. So, your output will be 3 times of that if you forget about the V t loss here. So, let us say I have a switch here instead of the diode connected device, then you will get three times V in or V dd. So, now, if I let us say I put a load here which means, I put a tap here and you start taking the water out from this bucket.

So, it will start emptying now, if I rate of this discharge is much faster than rate you are filling then it will be completely empty. So, which means there is a limit on the load you can put based on what frequency and capacitor size you are putting.

So, if I want to increase the load I have to either increase the frequency or which means I have to fill this bucket much faster or I have to increase the size of this bucket. If I am filling at the same rate and this source is your V dd. So, it has an infinite charge. So, you can keep filling your bucket and transferring into that output ok.

This was simple like V out equal to V dd. So, one important thing you need to remember here is that your final output will only depend on the flying capacitor not on the output capacitor. And how you differentiate between flying capacitor and load capacitor is by looking at the circuit how can we differentiate no, but if I do not write V out how will you know which one is connected to output.

So, what do you need for it to look like a flying capacitor? Why do we call it flying? So, this is connecting on both sides. So, it is taking the charge from V dd and dumping to the output capacitor, but if you look at the output capacitor, it is always connected to fixed ground ok. So, now, if I want to do let us say V out equal to 2 times V dd.

So, I will call it now CF means flying capacitor this is V out and ok. So, what would happen in this case, let us see during phi 1. So, phi 1 phi 2 are actually, let me draw here if this is phi sorry phi and phi bar when I say or you can call it phi 1 phi 2 whatever they are actually complimentary clocks. So, they should be non overlapped which means just like we had in the gate driver circuit for inductive switching regulators. So, why do we need non overlap clock here? If both are on, what will happen? The capacitor will be shorted and effective charge will become 0. So, the capacitor will fully discharge. So, it will disturb all the equations. So, during phi what is the charge? Or let us let me write voltage on the capacitor, it is C F how much?

Ok, if I call let us say V F phi equal to V dd and during phi bar what is it or if I call it VF bar how much is the voltage? Forget about the output capacitor for now.

What we are looking at is in steady-state correct. So, when do you consider this in a steady state? Any switched-capacitor circuit I mean this one or the other one. How will you know whether it is in a steady state or not? So, voltage will not change within that period, which

means in phi, whatever voltage is there in phi bar, the voltage will remain same. So, there will be no charge transfer. So, voltage will not change.

6

| Vo= 21Vdd                          |                                       |                                                                                                               |

|------------------------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------|

| Vur = = = v.                       | Diring B. Valtage M CF                |                                                                                                               |

| L'                                 | VFs = Vdd<br>dwlry \$<br>VFs = Vo-Vdd |                                                                                                               |

| P T T T T T T T T T                | w wy.                                 |                                                                                                               |

|                                    |                                       |                                                                                                               |

|                                    | icsa                                  | EE5325 Power Management Integrated Circuits<br>Integrated Circuits and Systems Group, Department of EE, IIT N |

|                                    |                                       | integrated circuits and systems broup, Deparation of EC, III is                                               |

| Vit = VEF                          |                                       |                                                                                                               |

| Vdd = Vo- Vdd<br>= Vo- 2Vdd = ided |                                       |                                                                                                               |

|                                    | case under no hory                    |                                                                                                               |

| Under loss undition.               |                                       |                                                                                                               |

(Refer Slide Time: 13:07)

So, this will be how much? V out. So, V out minus Vdd. Now VF phi equal to V F phi bar which means V dd equal to V out minus V dd this implies V out equal to 2 x of Vdd, ok. So, which means I will get output 2 x of your input. This is the ideal case under no loss under loss condition minus V loss ok.

So, this V loss will be in your switches mostly in the switches basically, this is acting as a switched-capacitor resistor. So, if your capacitor has some esr that will also contribute to say any resistive losses basically, you know its conduction losses. So, that will contribute to V loss which is in the conduction path. So, IR drop will be there and V loss is proportional to I load.

We usually use complimentary switches. So, let me do one thing. So, you can maybe make phi bar inverted or put a inverter on the other side. So, let me fix it. So, what happens? See, if it is a let us say one switch is PMOS other is NMOS, then it will be exactly same what we had. So, we are more used to having P and N in a switching regulator. So, that is why. So, what would happen? This will turn off and ok. So, how do we regulate the output? So, let us say I want 2 V dds I cannot even regulate 2 V dd because under load conditions your load is varying your output will vary. So, how do we regulate or let us say my input is 2 volt and I want output 3.5 volt. So, it is a 1.75 times your gain basically required here.

So, it will not regulate, is there any way I can regulate the output by still keeping let us say 2 V dd. So, obviously, under load condition you cannot get. So, the ideal condition is a 2 V dd which means, you will always get below to V dd even if you try to regulate it somehow let us say. Let us say I required 1.5 x then you will choose 2 V dd.

But how will we regulate at 1.5 x. So, there are some applications where you want like you do not want to regulate the output, but you may still want 2 V dd or V dd by 2 fixed ratios ok. So, let us say I want to boost my output voltage from 2 volt to 5 volt ok.

So, one way would be like ok, you just have a switching regulator and based on what ratio you require you can choose the duty cycle is straightforward ok. So, 50 percent you know it will give you 2 x here 2.5 times so, slightly more than 50 percent will give you that ok. So, another application let us say I want 1.5 x.

So, one possibility would be you do a 2 x from the charge pump and put a buck after that and it will give you 1.5 and if you remember that what is the problem in the boost. It is a bit slower because of right half plane 0. In this case you can easily get rid of that right half pane 0. So, that is one application.

Now, let us take case of a buck converter. So, let us say I want to regulate the output at 1 volt and my input is 10 volt. So, what is your duty cycle required 10 percent.

Which is almost at the border lower side, you hardly have any room to respond to transients ok. So, your duty cycle is almost saturated. So, what do you do, you divide by 2 from charge pump. So, your 10 volt becomes 5 volt and now from there you have 20 percent roughly duty cycles and get 1 volt up ok. So, in open-loop these are the applications, but sometimes we use in the close loop also these and we can regulate the output.