Power Management Integrated Circuits Dr. Qadeer Ahmad Khan Department of Electrical Engineering Indian Institute of Technology, Madras

Lecture - 08 Adding PTAT and CTAT voltages

<u>PTAT generation</u>: We know that collector current  $(I_c)$  of bipolar is given by

$$V_{We} = V_T \ln \frac{I_c}{I_s}$$

$$\frac{I_c}{I_s} \rightarrow -ve temp \cdot coeff$$

$$V_{Ve} = \frac{V_T \ln \frac{I_c}{I_s}}{1 + \frac{1}{2} + \frac{1}{2}$$

$I_c = I_s e^{V_{be}/V_T} \Rightarrow V_{be} = V_T \ln \frac{I_c}{I_s}$

Now  $V_{be}$  difference ( $\Delta V_{be}$ ) is given as  $\Delta V_{be} = V_T \ln \frac{I_{c1}I_{s2}}{I_{s1}I_{c2}}$ .

| $V_{5c_1} - V_{bc_2} = V_{T} \left[ \int_{\mathcal{L}_{s}} \frac{I_{c_1}}{F_{s_1}} x \frac{I_{s_2}}{I_{c_2}} \right]$    |       |

|--------------------------------------------------------------------------------------------------------------------------|-------|

| $\Delta V_{be} = V_{T} \left[ \lim_{t \to t_{1}} \frac{I_{c_{1}}}{I_{c_{1}}} \times \frac{I_{s_{2}}}{I_{c_{2}}} \right]$ |       |

| $\underbrace{\underbrace{\operatorname{Cate}}_{i}}_{i} = \frac{1}{c_i} \neq 2_{c_2}$                                     |       |

| $\mathfrak{l}_{\mathfrak{s}_1} = \mathfrak{l}_{\mathfrak{s}_2} \Rightarrow \mathfrak{Q}_1 = \mathfrak{Q}_2  (same size)$ |       |

| $\Delta V_{be} = V_T \int_{\mathcal{L}} \left( \frac{I_{c_I}}{f_{c_L}} \right)$                                          |       |

| $l_{c_1} \simeq m l_{c_2}$                                                                                               |       |

| ave = U7 ln (m)                                                                                                          |       |

| $\underbrace{Care.z}_{lasteria} \qquad I_{c_1} = I_{c_2}$                                                                |       |

| $Q_1 \neq Q_2$                                                                                                           |       |

| $Q_2 = MQ_1 = \int \Delta V_{ke} = V_T \ln(m)$                                                                           |       |

|                                                                                                                          | 870 B |

| NPTEL                                                                                                                    |       |

|                                                                                                                          |       |

In order to generate  $V_{be}$  difference ( $\Delta V_{be}$ ), we can have 2 situations as shown in above figure.

Case 1: Have different collector current for Q1 and Q2 with same size.

Case 2: Have same collector current for Q1 and Q2 with different size so that your  $I_{s1}$ ,  $I_{s2}$  can be different.

Most of the time we use this case-2. So, we always make  $I_{c1}$  equal to  $I_{c2}$  because this gives us more accurate results compared to the other one. So, we rely only on the difference between the reverse saturation current ( $I_s$ ) by introducing the area difference between the transistors.

So, now you can change the area or you can change the currents in the 2 bipolars and you can change the slope and get the bandgap. Since it is coming as "ln" term which means m required might be quite large. I mean you can just do the calculation, in order to get a 2 mV slope from  $86 \,\mu\text{V}$ .

86

$$\mu$$

V x ln(m) = 2 mV

ln(m) = 23

m = e<sup>23</sup>

m is quite large, which means your area will be bloated. So, usually we try to keep this m factor small and introduce another proportionality factor. Let us say m you may choose 10, so the size of one transistor will be 10 times of the other.

And then have another proportionality factor by modifying your circuit in such a way and that can be done through resistor divider. So, let us say with this  $V_T \ln(m)$ , I have another factor which is  $\frac{R_1}{R_2}$ . Now, you change the  $\frac{R_1}{R_2}$  ratio and get the required slope.

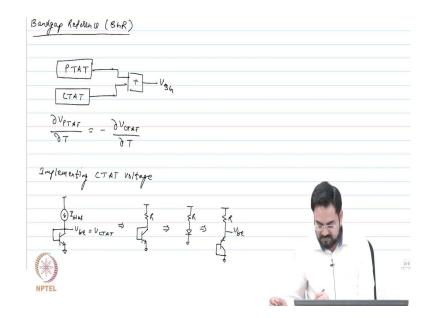

In order to generate bandgap, we need one voltage which is proportional to temperature and another voltage which is inversely proportional to temperature. And if we have same slope with opposite sign then they will cancel out and you will get the output as constant across temperature. V<sub>CTAT</sub> implementation:

If you connect your bipolar in a diode connected manner it will give you  $V_{be}$  and we know that  $V_{be}$  is inversely proportional to temperature. And the circuit diagram is shown in below.

And most of the time we use PNP because in the standard CMOS process we get the parasitic bipolar and you do not get active bipolars.

There is a difference between parasitic and active; active bipolar is basically fabricated through the process and it is mostly vertical actually. And you get the parasitic bipolar by default when you fabricate the PMOS and NMOS. So, by default you get the p-diffusion, n-diffusion and p-diffusion.

So, three diffusions you get and all three make your collector, base and emitter and you get basically a PNP device. And since this collector is built on P-type substrate and substrate is mostly grounded. So, you get a bipolar by default whose collector is grounded or connected to substrate. You do not have a freedom to connect the collector anywhere else, but you have to ground it.

So, base is N-type here, and if you tie the base to the ground then we get the same diode behaviour. So, the difference between active and parasitic is the gain ( $\beta$ ) actually. The  $\beta$  of parasitic bipolar is very bad compared to the active. Active may have  $\beta$  like more than 100 or so, bur these parasitic bipolar may have  $\beta$  much less than 10 or so.

That's why mostly we use these substrate PNPs in order to design the bandgap for a standard CMOS. But if you have a process which has active bipolar then you are free to use. In my circuits I will draw the diode instead of drawing PNP or NPN. So, by default you understand that you have to replace that with a diode connected NPN or diode connected PNP.

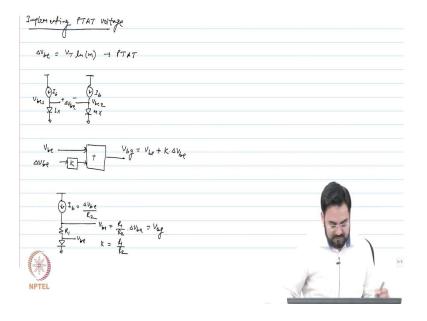

## V<sub>PTAT</sub> implementation:

Circuit diagram is shown in below figure. And the  $V_{be}$  difference ( $\Delta V_{be}$ ) can be used as PTAT.

But slopes are different, so you need to scale that. So,  $V_{be}$  is fixed and  $V_{be}$  can't be scaled but  $\Delta V_{be}$  needs to be scaled to match the slope of your  $V_{be}$ . Let's say  $\Delta V_{be}$  needs to be scaled by K. So, we get

$$V_{bg} = V_{be} + K \Delta V_{be}$$

So,  $V_{be}$  is straight forward and we have to see how to generate the scaled down version of  $\Delta V_{be}$ . One possibility could be instead of taking the difference of two voltages, first I will generate

the current  $I_b = \frac{\Delta V_{be}}{R_2}$  and dumb into the resistor as shown in above figure.

So, now we get  $V_{bg} = V_{be} + K \Delta V_{be}$  where  $K = \frac{R_1}{R_2}$ .