Power Management Integrated Circuits Dr. Qadeer Ahmad Khan Department of Electrical Engineering Indian Institute of Technology, Madras

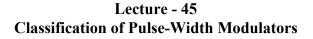

The above image shows the simulated result of the switching converter in both CCM and DCM. The simulation is done in an open-loop and keeping the duty cycle constant. If we keep the duty cycle constant and keep reducing the load current then at the moment when the switching converter enters into DCM, we can see that the output voltage will start increasing and start approaching  $V_{IN}$ . We can see there is hardly any voltage change in the output voltage in CCM and minor change is due to the IR drop.

|                                                | ics | EE5325 Power Management Integrated Cir<br>Integrated Circuits and Systems Group, Department of EE | cuits<br>, IIT N |

|------------------------------------------------|-----|---------------------------------------------------------------------------------------------------|------------------|

| PWM Modulator                                  |     |                                                                                                   |                  |

|                                                |     |                                                                                                   |                  |

| Sigle edge alust edge<br>Modulation Madulation |     |                                                                                                   |                  |

| Medulation Madulation                          |     |                                                                                                   |                  |

| f f                                            |     |                                                                                                   |                  |

| elget elget                                    |     |                                                                                                   |                  |

| Trailing loading<br>edge ledget                |     |                                                                                                   |                  |

## **PWM Modulator**

We know that the switching regulator works on the principles of the PWM. The control voltage from the feedback loop has to be converted to a PWM clock which will regulate the output. PWM modulator can be divided into two categories, single edge modulation, and dual-edge modulation. Single edge modulation can further be divided into trailing edge modulation and leading-edge modulation.

|              |                                                                                |        | NPT     |

|--------------|--------------------------------------------------------------------------------|--------|---------|

|              | •                                                                              |        |         |

| Sigle edge   | alust edge                                                                     |        |         |

| Modulation   | Mendulation                                                                    |        |         |

|              |                                                                                |        |         |

| +            |                                                                                |        |         |

| Trailing los | 2                                                                              |        |         |

| edge edg     | /                                                                              |        |         |

|              |                                                                                |        |         |

| Trailing E.  | e Modulation                                                                   |        |         |

| Vane         |                                                                                |        |         |

| 1 A          | A Very Very                                                                    |        |         |

| 11           | Vetri                                                                          |        | 3 3.0   |

| Tim          |                                                                                |        | 1 A     |

| шш           | I is it duty cycli is dangest them<br>only trailing edge moves while leading a | In tak |         |

|              | I trang age moves more ready o                                                 | WEITH  |         |

|              | 2° 20 52                                                                       |        | ~ ( A ) |

|              |                                                                                |        |         |

The connection of signals to the comparator is shown in the above image.

## **Trailing-Edge Modulation**

Waveforms of  $V_{RAMP}$ ,  $V_{PWM}$  for different values of  $V_{CTRL}$  are shown in the above image for Trailing-Edge modulation. As you can see, the duty cycle is proportional to the value of  $V_{CTRL}$  and only the trailing edge of the PWM signal moves upon changing the value of  $V_{CTRL}$  and the leading-edge remains fixed.

| Leaking Edge Modulation |                                                              |        |    |

|-------------------------|--------------------------------------------------------------|--------|----|

| wang                    |                                                              |        |    |

| vpm if d                | nty cycle is chapped shew                                    |        |    |

| lead -<br>is fire       | aby cycle is chapped dhew<br>a cappe moves while train<br>d. | d only |    |

| about Edge Modulation   |                                                              |        |    |

|                         |                                                              |        | 35 |

|                         |                                                              |        | M  |

## Leading-Edge Modulation

Waveforms of  $V_{RAMP}$ ,  $V_{PWM}$  for different values of  $V_{CTRL}$  are shown in the above image for Leading-Edge modulation. As you can see, the duty cycle is proportional to the value of  $V_{CTRL}$  and only the leading-edge of the PWM signal moves upon changing the value of  $V_{CTRL}$  and the trailing-edge remains fixed.

| Leuking Edge Mo  | abtim         |                                     |         |       |

|------------------|---------------|-------------------------------------|---------|-------|

| um               | 4             |                                     |         |       |

|                  | -Vital        |                                     |         |       |

| VPM              | ⇒ it duty y   | is is charged the                   | w       |       |

|                  | level of edge | d is chapped dhe<br>moves while tra | ing whe |       |

|                  |               |                                     |         |       |

| alkal Edge Modul | etim          |                                     |         |       |

| $\wedge \wedge$  | Fratt         |                                     |         |       |

| VPIN THE         | a if duty of  | y cle is chapped all                | den .   | 1 210 |

|                  | both edge     | rus is chapped 44.<br>move.         |         | 1 Mar |

## **Dual-Edge Modulation**

Both trailing edge and leading edge moves in dual-edge modulation upon changing the  $V_{CTRL}$ .  $V_{RAMP}$  should be in a triangular shape for both edges of  $V_{PWM}$  to move when  $V_{CTRL}$  changes. Waveforms of  $V_{RAMP}$ ,  $V_{PWM}$  for different values of  $V_{CTRL}$  are shown in the above image for Dual-Edge modulation. Off time decreases and the duty cycle increases on increasing the  $V_{CTRL}$ . The benefit of dual-edge modulation is that it is sampling  $V_{CTRL}$  at double rate compared to trailing edge modulation and leading-edge modulation. So delay is less in dual-edge modulation when  $V_{CTRL}$  changes. Frequency is changing in dual-edge modulation when instantaneous change occurs in  $V_{CTRL}$  and both edges move but go back to the original value in steady-state. If we are using a random load that is switching then duty cycle frequency will have a lot of harmonics which is not good for noise-sensitive applications. So if we are expecting output voltage ripple to be of fixed frequency then we prefer leading-edge modulation or trailing edge modulation rather than the dual-edge modulation.