## Power Management Integrated Circuits Dr. Qadeer Ahmad Khan Department of Electrical Engineering Indian Institute of Technology, Madras

## Lecture- 19 Dominant Pole Compensation at No-Load

In previous lecture we looked at how we find the value of your compensation cap for Dominant Pole Compensation. We continue with that and we will just consider one more example.

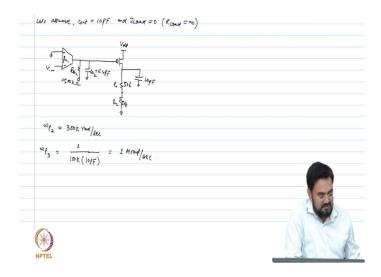

Let's assume your  $C_{out} = 10 \text{ pF}$  and  $I_{load} = 0$ .  $I_{load} = 0$  means  $R_{load} = \infty$ . The circuit diagram is shown in below figure.

I am just assuming feedback factor( $\beta$ ) is 0.5 and choosing feedback resistors as 50 k $\Omega$  each. If I want 1.5 V output voltage then V<sub>ref</sub> should be 0.75 V.

So, one thing you need to remember if you change the load then it will change your output resistance and your output pole will get affected. So,  $C_{out} = 10 \text{ pF}$  and  $R_{out} = 100 \text{ k}\Omega$ , so we will get  $\omega_{p3}$  at 1 Mrad/sec.

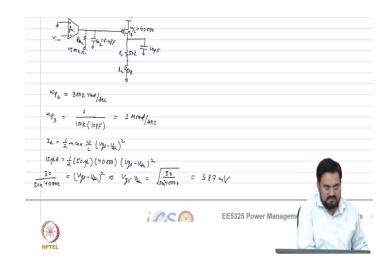

To supply maximum current of 10 mA by this pass element, we got the ratio  $\frac{W}{L} = 40,000$ . At no load I<sub>D</sub> = 15 µA and at this current the overdrive voltage is 3.8 mV as shown in below figure.

So,  $g_{m3} = \frac{2I_D}{V_{ov}} = \frac{2 \times 15 \mu}{3.87 m} = 7.7 \text{ mS}$

Student: Sir, while calculating  $\omega_{p3}$  we forgot to consider the output resistance of MOSFET in  $R_{out}$  .

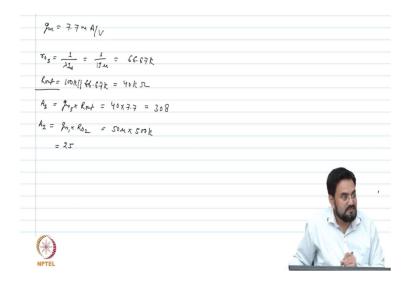

Ok. Since pass element is a minimum channel length device, so if I consider channel length modulation ( $\lambda$ ) is approximately 1, then  $r_{o3} = \frac{1}{\lambda I_D} = \frac{1}{15 \,\mu} = 66.67 \, \text{k}\Omega$ . After considering this we will get  $R_{out} = 40 \, \text{k}\Omega$ . So,  $C_{out} = 10 \, \text{pF}$  and  $R_{out} = 40 \, \text{k}\Omega$  gives  $\omega_{p3}$  as 2.5 Mrad/sec.

$A_2$  = gain of your first stage (Dc gain of op-amp)

$A_3 =$ gain of your second stage

So, first stage gain is low and output stage gain is higher because pass element  $g_m$  is very large and  $R_{out}$  is also very large. And if you calculate the same output stage gain at 10 mA you will see that it will drop actually.

| 9m = 7.7 m A/V                                                                    |  |

|-----------------------------------------------------------------------------------|--|

| $\gamma_{\theta_3} = \frac{1}{\lambda I_{al}} = \frac{1}{15\mu} = 66.67 \text{K}$ |  |

| knf = 100k11 66.67k = 40K52                                                       |  |

| A3 = 1/3 x Rout = 40x7.7 = 308                                                    |  |

| A2 = Myx Roz = Soux Sook                                                          |  |

| = 25                                                                              |  |

| A0 = 7700 = 77dB                                                                  |  |

| BAO = 7700 = 7003.                                                                |  |

| 2                                                                                 |  |

|                                                                                   |  |

| A                                                                                 |  |

So, overall gain is  $25 \times 308 = 7700 = 77 \text{ dB}$

And If you consider the feedback factor( $\beta$ ) then it will further drop by 6 dB. So, loop gain (A $\beta$ ) is 7700 x 0.5 = 3850 which is close to 70 dB.

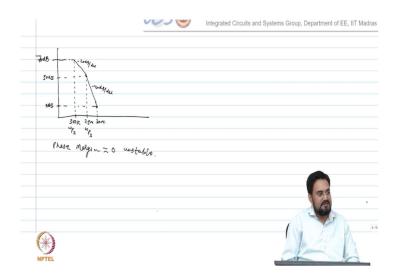

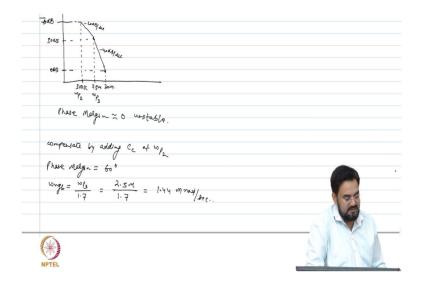

The bode plot for loop gain is shown in below figure.

Note that exact  $\omega_{ugb}$  we will get as 44.5 Mrad/sec. And the phase at  $\omega_{ugb}$  is almost 180° because both poles will have a 90° phase contribution at  $\omega_{ugb}$ . So, phase margin is 0° which implies that system is unstable.

If I want to compensate it, shall I add the capacitor at output or at  $\omega_{p2}$ ?

Student: At  $\omega_{p2}$  because to compensate at  $\omega_{p3}$  we will require a very large cap.

Yeah, when you compensate at the output, your worst case will be the maximum load because at the maximum load your  $R_{out}$  will be very low. So, you require a very large cap to make it dominate. But if you put the cap at  $\omega_{p2}$ , then your worst case is the light load because at the light load your output pole will be at lower frequency.

So, if your dominant pole is at  $\omega_{p2}$ , then as you increase the load your second pole will be pushing at higher frequency and it will further improve your phase margin. So, if you compensate at a light load by putting the compensation cap at  $\omega_{p2}$ , then for higher load it will be automatically compensated because your second pole will be moving at higher frequency. And that is what you want. You want to move your non-dominant pole outside your  $\omega_{ugb}$ .

So, I want to push this  $\omega_{p3}$  outside your  $\omega_{ugb}$ , which means  $\omega_{p2}$  has to be reduced. And to get 60° phase margin your non-dominant pole should be roughly 1.7 times of your  $\omega_{ugb}$ .

DC loop gain (A $\beta$ ) is 70 dB which is roughly 3500.

So,  $\omega_{p2}$  after compensation is at 400 rad/sec. To place  $\omega_{p2}$  at 400 rad/sec the compensating cap (C<sub>C</sub>) required is 5 nF and the calculations is shown in below figure.

$$\begin{split} & \overset{\mathrm{W}}{f_{\mathrm{L}}}\left(\operatorname{comptualized}\right) = \frac{1 \cdot 44 \,\mathrm{m}}{\beta \,\mathrm{A}_{\mathrm{D}}} = 400 \,\mathrm{Med}/\mathrm{Ae} \\ & \overset{\mathrm{W}}{f_{\mathrm{L}}} = \frac{1}{R_{02}} \left(\frac{1}{C_{\mathrm{L}} + C_{\mathrm{L}}}\right) = 400 \,\mathrm{Med}/\mathrm{Ae}. \\ & \mathrm{Lo}_{\mathrm{L}} + C_{\mathrm{E}} = \frac{1}{S00 \,\mathrm{R} \,\mathrm{R} \,\mathrm{H}_{\mathrm{PD}}} = \frac{1}{2 \times 15^{9}} = \frac{10^{-9}}{2} = S \,\mathrm{m} \,\mathrm{F}. \end{split}$$

CL = JNF

This 5 nF is again a very large cap and it is almost impossible to put on-chip. You can put, but then all the area will be occupied by your capacitor compared to your circuit areas ok, 90% area will be taken by your capacitor which is not preferable.

Which means if you want to do the dominant pole compensation, you will again require very large cap, whether you put it at the second stage or at first stage. Obviously, at the second stage it will require even larger which is only possible with the external cap like order of microfarad. 5 nF is possible to put on-chip, but again it will take a lot of area. So, practically it is not feasible, and we never put order of nanofarad of cap on-chip until unless you are only designing the regulator chip. But most of these regulators are part of a bigger system, and you do not want to bloat the area just by increasing the size of your regulator.

So, 5 nF is quite large to implement on-chip. So, we look for alternate way of reducing the cap size. So, we require miller compensation.