## Analog Integrated Circuit Design Prof. Nagendra Krishnapura Department of Electrical Engineering Indian Institute of Technology, Madras

## Lecture - 14 Two stage miller compensated opamp-2

(Refer Slide Time: 00:07)

| Analog Integrated Circuit Design—Lecture 14                               |

|---------------------------------------------------------------------------|

|                                                                           |

|                                                                           |

|                                                                           |

|                                                                           |

| Opamp realization—Two stage opamp                                         |

| <ul> <li>Two stage opamp poles and zeros; example calculations</li> </ul> |

| , , , , , , , , , , , , , , , , , , ,                                     |

|                                                                           |

|                                                                           |

|                                                                           |

|                                                                           |

| NPTEL 2 200                                                               |

| Nagendra Krishnapura Analog Integrated Circuit Design                     |

Hello and welcome to lecture 14 of Analog Integrated Circuit Design. In the previous lecture, we tried to make a better opamp and we were better opamp through the analysis to see whether it is really better or not.

(Refer Slide Time: 00:24)

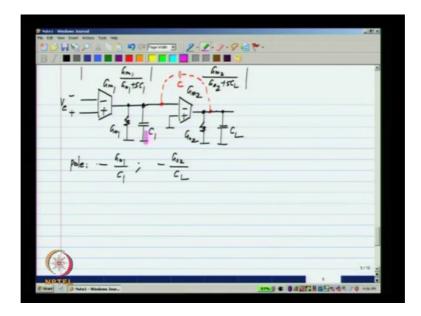

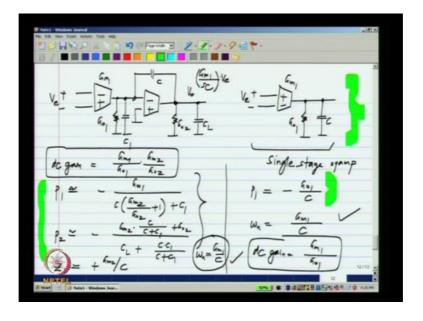

And the topology of the opamp that we came up with was like this, the first trans conductor converts the input voltage to a current and that is passed through a current control voltage source made using a second opamp which is simply this Gm 2 and CL and the current to voltage conversion happens because of this C that is connected from the input to the output of this opamp.

This is basically a current controlled voltage source of a trans impedance 1 over SC. We derived the transfer function of this opamp and we saw that the transfer function has 1, 0 and 2 poles and we were trying to make intuitive sense of the pole values that we obtained and to do that what we also did was we removed this C and evaluated the pole values which turns out is very easy to do Go 1 by C 1 and Go 2 by CL ok.

(Refer Slide Time: 01:15)

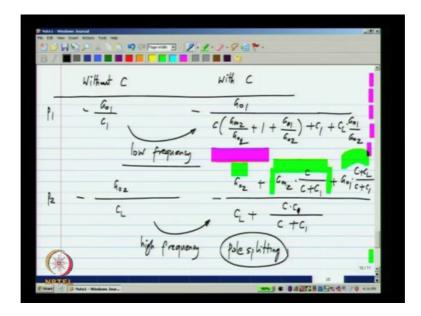

Now, when we do have the C, we will get these pole values; this complicated thing here and that complicated thing there and this first one, we made an intuitive sense out off by saying that it is Go 1 divided by some other capacitance. Initially we had Go 1 by C1. Now, we have Go 1 by C1 plus Miller multiplied C and we also saw why Miller multiplication happens.

Similarly, now for the second pole it is Go 2 by CL. First of all even the numerator has changed it is Go 2 plus some other terms which represent conductances and in the denominator we have CL plus all of this stuff. So, does this make sense? Indeed it does as we will see shortly.

(Refer Slide Time: 02:02)

So, again let me repeat the opamp that we have Gm 1 Go 1 C 1 Gm 2 Go 2 and CL and we have C from there to there ok.

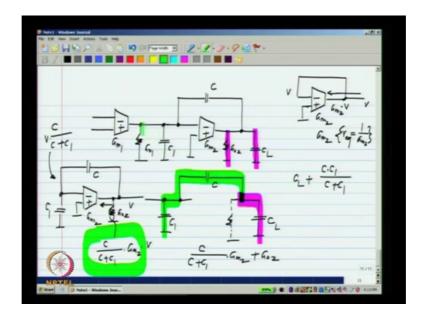

So, now originally the conductance here was Go 2; now it appears to be something different. Originally, the capacitance here was CL. Now it again appears to be something different ok. So, again what we can do is to examine the network around this and you also know that poles are characteristic of a circuit, they have nothing to do with where the input is applied. So, we can examine the circuit with a 0 input and determine the poles.

So, when we have 0 input this transconductor of Gm 1 is as good as not being there. So, the circuit we have is something like that ok. I will draw only the capacitors C C 1 and CL and I do this and I also try and see what is the capacitance associated with this node that is from this node to ground and I do this because this is where Go 2 was right. This is where Go 2 is. Originally, we had only Go 2 and CL from this node to ground. Now, we have some conductance and some more complicated network of capacitances, but it is not all that complicated; all we have is this CL in parallel with the series combination of C and C 1.

So, what does that give you? The total capacitance will simply be CL plus C 1 by C plus C 1 and if we go back to the expression you see that the denominator is exactly that it is simply the load capacitance plus the series combination of C and C 1 that is all ok.

Similarly, now the conductance the term in the numerator seemed to contain some Gm 2 ok; whereas, Gm 2 is the transconductance. How did this happen? I think all of you are aware that you can take a trans conductance Gm 2 or a voltage controlled current source and make it appear like a conductance using feedback ok. What does the trans conductance do?.

If I have some voltage here, it draws a current Gm 2 times V. If I connect an input and the outputs together, what does it mean? If I have a voltage here, it draws the same current from that voltage and what is that? That is nothing but a resistor or a conductance ok. If you have a voltage and you are drawing there is an element which draws a current that is proportional to that voltage that is nothing but a conductance.

And the conductance of this is Gm 2 or the resistance is 1 over Gm 2 ok. So, something like this must be happening that is the transconductor is in feedback and that is why we are ending up with a conductance which has a term containing the trans conductance Gm 2 and clearly there is indeed feedback here, you see that there is feedback with C and C 1 around Gm 2 ok.

Now, I will draw only that part of the network ok. If I apply a voltage V, the voltage here will be V times C by C plus C 1 ok. It is simply a capacitive division of the voltage V and the current drawn here will be that voltage times Gm 2. So, that is nothing but C by C plus C 1 times Gm 2 times V.

So, clearly this entire network as far as the contribution of the transconductance is concerned looks like a conductance of that value ok. So, the transconductance because it is in feedback contributes a conductance of C by C plus C 1 times Gm 2. In this case, it is divided Gm 2 because all of this way was fed back to the input. Here only a fraction of V is fed back to the input.

So, it is smaller than Gm 2, but none the less are related to Gm 2 ok. So, that is the conductance contributed by Gm 2; in addition to this, you have Go 2 itself over there. So, we expect that we will have C by C plus C 1 times Gm 2 plus Go 2 and indeed if you look at the expression we have Go 2 plus the effect of Gm 2 being in feedback ok.

Now, we also have this extra term because what we have here is not only C 1, we have Go 1 in parallel ok. So, that gives you some extra terms because in term Go 1 at all, you

would have only this capacitive network. We also have Go 1 here and that gives you some conductive portion which is related to Go 1 ok.

But typically you expect that Gm 2 is much more than Go 1 and Go 2. So, in fact, the dominant conductance is expected to be this middle term here ok, this one alone and the other 2 will be smaller ok. So, although again whereas, the expression looks complicated; it is very easy to make intuitive sense out of it.

It is again some conductance by some capacitance the conductance happens to come from the output conductance of the second stage as well as the trans conductance being in feedback. Similarly, the capacitance comes from the load connected to the second stage which is CL plus the series combination of C and C 1 because that is how they are connected in the circuit ok. Also another thing, we observed was that this P 1 which was minus Go 1 by C 1 without C moved to a lower frequency because the apparent capacitance increased.

Now, what happens to P 2? It is Go 2 by CL and here, we see that both numerator and denominator have changed. The numerator has increased, the denominator also has increased. But it is important to keep in mind that Gm 2 is expected to be much much more than Go 2 ok.

In fact, that is how you get gain. The gain of the second stage is Gm 2 by Go 2 and you expect the dc gain to be at least 10, if not in the many tens or hundreds ok. Whereas, the capacitance has become CL plus some value which you generally expected to be of the same order of CL, same order as CL or even smaller ok.

So, the denominator increases, but only modestly; the numerator increases enormously. So, it turns out that this P 2 moves to a high frequency compared to the case where we did not have a C. We considered the case without C only because the poles were easy to calculate and also it turns out that it is a common scenario, you have 1 amplifier after another and if you cascade a number of amplifiers you get a number of poles from each amplifiers output ok.

Now, in our case we have 2 amplifiers 1 after another and our opamp looks like such a structure with 2 amplifiers and a capacitor connected from the input to output of the second stage and when you do that it turns out that 1 pole moves to the lower frequency

and another pole moves to a higher frequency. So, such a thing is known as Polesplitting ok.

So, it turns out that it is. In fact, a useful thing to have when we are trying to make opamps because after all what will we want? We wanted the opamp to behave like an integrator that is a single pole system and we also saw from stability criteria that if you have extra poles at all they should be at much higher frequencies.

Now here, in this case what happens is one of the poles moves to higher and higher frequencies and that is a good thing for an opamp, as we will see also in future analysis ok. So, in summary, the new opamp that we came up with as 2 poles and a 0 and the poles are given by these expressions and the 0 all we already determined, it is at plus Gm 2 divided by C ok.

(Refer Slide Time: 11:08)

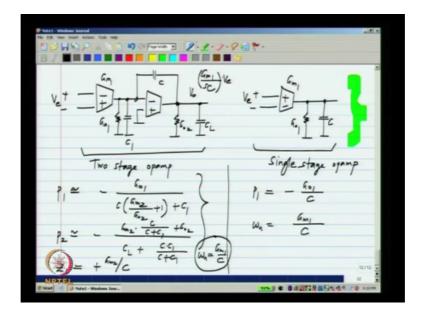

So, this because it has 2 transconductance stages one after another. It is known as Two stage opamp and our earlier opamp which has a single trans conductance stage loaded by a capacitor, this is known as a Single stage opamp. And in each of these cases, we could use voltage buffers after these opamps, but like I mentioned earlier voltage buffers are hardware to make in the CMOS technologies especially, with low voltages, low supply voltages. So, we typically tend to use these opamps without explicit buffers.

These things will become clearer when we come to circuit realization of these opamps and this has 2 poles. I will write only the approximate values here. It also has a 0 which is at plus Gm 2 by C; whereas, the single side opamp, if you recall it has a single pole at minus Go 1 divided by C ok.

Now, what is the unity gain frequency of the single side opamp? That is nothing but Gm 1 divided by C and what is the unity gain frequency of the 2 stage opamp? It is also Gm 1 by C because after all recall how we came up with this topology. We have in this transconductance Gm 1, whose output current is passed through this capacitor ok; by putting the capacitor and feedback around a second opamp.

So, that we for my current controlled voltage source; So, the approximate transfer function from the input to the output is still Gm 1 by S C times Ve. So, that means, that the unity gain frequency here is Gm 1 by C as well ok. Now this can also be verified very easily.

(Refer Slide Time: 14:36)

If we draw the magnitude response of the 2 stage opamp, it will have a dc gain of Gm 1 Gm 2 by Go 1 Go 2 which is the product of the dc gain of the 2 stages.

And there is a pole and at that point, there will be a breakpoint and the gain drops at 20 dB per decade ok. And then at some frequency, there will be a second pole P 2 and then

some other frequency, there will be a Z; there will be the 0 Z 1 ok. I have assumed that P 2 is smaller than Z 1 which may or may not be the case.

Now here you see that the behaviour is first order all the way down to P 2 and this is the 0 dB line. I am assuming that their behaviour is first order all the way down to the 0 dB line. This way anyway no has to be true for good stability ok; from our earlier study of bode plots and quits criteria, we have seen that the system has to maintain, the loop gain has to maintain first order dependence on frequency all the way down to unity loop gain frequency.

Now, if we place this opamp our Two stage opamp, in unity feedback. The unity loop gain frequency of this feedback loop is nothing but the unity gain frequency of the opamp itself. So, we will assume that we have made a unity feedback configuration like this.

So, in this case, the unity loop gain frequency will be the unity gain frequency of the opamp and first order behaviour has to be maintained all the way down there and because this is first order behaviour, this frequency is easily seen to be the product of this dc gain and this pole times the magnitude of P 1 and if we evaluate that P 1 is nothing but Go 1 by ok.

So, that cancels with that and this approximately cancels with that and this C times Gm 2 by Go 2 plus 1 is much larger than C 1. So, this C 1 can be neglected and then, there is Gm 2 by Go 2 term cancels Gm 2 by Go 2 plus 1 because Gm 2 by Go 2 is a number that is much more than 1. So, the unity gain frequency approximately is Gm 1 by C ok.

Now, remember this is the unity gain frequency that we were trying to implement. So, it is not surprising at all that we get the same number, but just wanted to show that when you calculate it, without knowing anything about the circuit; you simply calculate it as a product of the dc gain and the first pole assuming that first order behaviour is maintained all the way down to 0 dB gain, you will get the same answer ok.

And it is nothing but the unity gain frequency of the single stage opamp we start off with ok. After all we made this as an improvement to that one without changing the unity gain frequency ok. Is this fine? Now, so, what is the advantage of this after all? The advantage of the Two stage opamp is that the single size opamp has a dc gain which is Gm 1 by Go

1; whereas, the 2 stage opamp as a dc gain which is Gm 1 by Go 1 times Gm 2 by Go 2 ok.

So, the dc gain of this can be significantly larger than a dc gain of that one; both have the same unity gain frequency and this has a single pole whereas, this has multiple poles and zeros. So, while stability is unconditional with a single stage opamp, we have to worry about the stability of the 2 stage opamp because it has multiple poles and zeros. And as I have mentioned earlier, stability for us not only means not oscillating.

It is not just that; it also has to be well behaved we should not have ringing and so on in this step response ok. We will see the conditions for that soon, but the advantage is very clear. We get the dc gain of the single stage here; whereas, we get dc gain of 2 stages and we have designed it. So, that the unity gain frequencies are the same. So, we have to compare the other things ok.

Now, besides this there is also another advantage of using a 2 stage opamp compared to a single stage opamp. Let me copy these things over.

(Refer Slide Time: 20:21)

And that has to do with what happens when the load is resistive that is let us say we have an external load which we also connect to this and connect to that one ok and in general; when you do that it is expected that the load conductance GL is much more than Go 1 that is R L is much smaller than Ro 1.

Similarly here, GL can be much more than Go 2 ok. So, the dc gain in this case will be Gm 1 by Go 1 times Gm 2 by Go 2 plus GL. Similarly here, the dc gain will be Gm 1 by Go 1 plus GL and GL will dominate Go 1 GL will dominate Go 2 there ok.

Now, clearly you can see the problem here. In case of a single stage opamp if you do have a resistive load, you have to make this Gm 1 much much more than the load conductance. So, that you get a significantly less dc gain ok. The dc gain required may be of the order of thousands or even higher and when you try to implement a large value of Gm you end up dissipating a lot of power and that is a serious problem for circuit design.

Here, what can be done is Gm 2 does not have to be much much more than GL. It has to be more than GL. But not by factor of 100 or 1000, but it could be more by only a factor of 10. Let us say that is because you can still keep Gm 1 by Go 1 very large and get a dc gain that has a large respectable value ok.

In other words, you place the burden of getting a large dc gain on the first stage. The first stage is isolated from the load. So, it will not be affected by how low this value of R L is and the second stage has to provide only a modest gain. So, when you have a resistive load, this is really only the feasible alternative because if you try to use this it is possible. But you will have to end up using such a large Gm that it will be very wasteful of power ok.

Now, what about stability with the Two stage opamp. I said that you have multiple poles and zeros. So, you have to worry about stability.

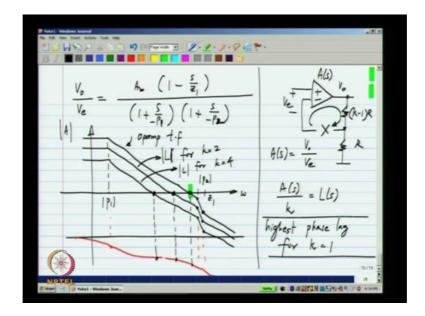

So, we have the transfer function of the opamp to be A naught which is the dc gain. I will write it in this form 1 minus S by Z 1 ok. So, let me I do it like this so, that minus P 1 and minus P 2 are positive numbers ok. Now, what about stability? Stability margins and so on are determined by loop gain and the loop gain itself depends on the feedback loop that you place the opamp in ok.

So, let us say I realize an amplifier of gain k ok. The loop gain of this let us say the transfer function of the opamp itself is some A of S. A of S is Vo by Ve. The loop gain is what I get by breaking the loop and going around it and seeing what comes back there. So, that will be nothing but A of S divided by k ok. This we have seen earlier. So, this is the loop gain. Now, so, the loop gain depends on the value of k which means that it depends on the amplifier that we are trying to implement ok.

Now, let us say we take the opamp and the gain of the opamp A of S of the opamp has this magnitude ok. So, this is modulus A that is modulus V naught by Ve and it has a pole at P 1 and it has a pole at P 2 and a 0 at Z 1 ok.

This is the gain or the transfer function of the opamp and what will be the loop gain depending on the value of k this curve will be shifted down by 20 log k on the bode plot ok. So, if k equals 1, this itself is the loop gain; if k equals 2, it will be like that and similarly, if k equals 4, it will be like that and so on ok. So, this will be the magnitude of L for k equals 2, the magnitude of L for k equals 4 and so on.

Also, if I plot the phase response; what happens? There is a 45 degree phase shift at the first pole and then, the phase of is just minus 90. At the second pole there is another 45 degree shift and at the 0 there is another 45 degree shift because this is a top plane 0 ok.

So, we will not worry about the details of the phase right now, but what I at the point I want to make is that we have seen that the stability margin depends on what happens at the unity loop gain frequency ok. For the 3 cases I have considered k equals 1; k equals 2 and k equals 4. These are the unity loop gain frequencies and you can see that the phase keeps going down monotonically for a function like this. So, we are interested in the phase margin that is how far the phase lag is away from a minus 180 degrees phase lag ok.

So, clearly it gets worse for lower values of k ok. This is the worst, it has the maximum phase lag. This is better, it has less phase lag. This is even, it has the least phase lag ok. So, we have the highest phase lag for k equals 1 ok.

Now, this is relevant because normally when you design an opamp without any further information, you simply have to assume some value of k; obviously, the value of k that you have to assume it is the worst case which is in this case 1 that is you assume that whoever is going to use your opamp can use it with various values of k and you design it for the worst case and the worst case happens to be 1. So, if k is 1 the loop gain is nothing, but the opamps gain itself.

So, it is easy; anyway you can design the whole thing without worrying about which feedback loop that is use evaluate the gain of the opamp and assume that that itself is the loop gain and I just hit first stability ok. Now this is not a general procedure, when you do know what value of k you have to design it for you design it for that particular value ok; you do not design it for the worst case value. It is only when you do not know that you design it for the worst case value, we will assume for the purpose of this lecture that will design it for k equals 1. So, if we have k equals 1.

(Refer Slide Time: 28:49)

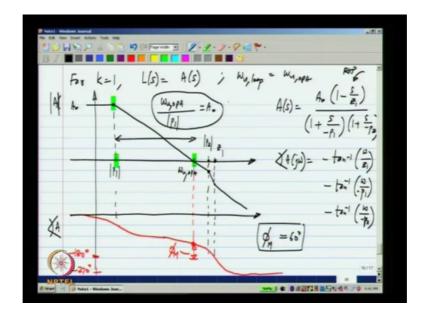

The loop gain equals the gain of the opamp or the unity loop gain frequency equals the unity gain frequency of the opamp ok.

Now, let us again examine the function that we have the magnitude and phase A of S is a naught times 1 minus S by that 1 plus S by minus P 1 plus S by minus P 2 ok. So, as I plotted earlier, you start with A naught and then, you have a 20 dB per decade slope in the magnitude plot. We have to make sure that these other poles appear beyond the unity loop gain frequency ok.

This we have seen during our discussions of stability analysis and also these zeroes have to appear, beyond the unity loop gain frequency ok. So, this is the condition that we must satisfy and it should be beyond by a certain value and how do we determine that value? For that we this is the magnitude of A, we plot the angle of A which is also the angle of loop gain in this case. So, in our case we have a right half plane 0 ok.

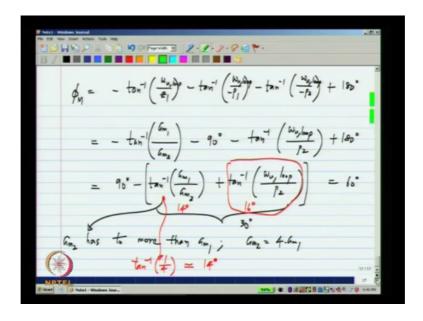

Now, the right half plane 0 introduces phase lag ok; if you write the expression for the phase of this angle of A of j omega will be minus tan inverse omega by Z 1 minus tan inverse omega by P 1 minus tan inverse omega by minus P 2 ok. Here, P 1 and P 2 are the poles which were negative number. So, this is how I have written it.

So, each of these contributes to phase lag and the total phase lag happens to be minus 270 degrees. Now, what is it that we want? At the unity loop gain frequency which for k equals 1 is the unity gain frequency of the opamp itself.

We should make sure that this margin which is the margin between minus 180 degrees and the actual phase at the unity loop gain frequency is sufficiently high, that is called the Phase margin and again in absence of any specific information will assume that the phase margin has to be lets says 60 degrees or so ok. So, this again is not a sacred number you could have a phase margin anywhere from 30 degrees to 80 degrees or whatever you want based on the context. But generally we assume that 60 degrees is a good number and use that ok.

(Refer Slide Time: 32:19)

Now, what does this mean? The total phase margin is the total phase lag which is minus tan inverse omega by Z 1 minus tan inverse omega by P 1 minus tan inverse omega by minus P 2 plus 180 degrees; it is the distance from 180 degrees.

So, first of all what omega are we talking about here? This is the omega u loop, unity loop gain frequency. That is where the phase margin is measured and the unity loop gain frequency is minus tan inverse Gm 1 by C and the 0 Z 1 is that Gm 2 by C ok. So, this is the first term and it simply reduces to Gm 1 by Gm 2 ok.

The second one, this is the ratio of omega you loop divided by P 1 and the tan inverse of that. Omega u loop is here and P 1 is there and they are very widely separated. What is the factor of separation between these 2? It is very easy to see.

This is 20 dB per decade drop. So, this is nothing but the separation between these 2 is the same as this number A naught ok. The ratio of these 2 numbers omega u o P a by P 1 is AA naught. This is something we know already omega u o P A can be approximately calculated as A naught P 1, when the roll off is predominantly a first order ok.

Now, because of that this is tan inverse of a large number. So, this is simply minus 90 degrees that can also be seen from the plot the phase drops down to minus 90 and stays that way for stays that way ok. This is the phase lag due to P 1. Now because P 1 is far from omega o P A, it would have reached 90 degrees somewhere here and then it stays on 90 degrees all the way there the contribution due to P 1 ok.

And finally, we have minus tan inverse omega u loop by P 2 this is something that has to be calculated. I just leave it as it is omega u loop by P 2 plus 180 degrees and this is nothing but 90 degrees minus tan inverse Gm 1 by Gm 2 minus tan inverse omega u loop by P 2 ok.

Let me write it as minus the sum of these two. This is the phase lag due to the right half plane 0; this is the phase lag due to the second pole ok. And we would like this to be let us say 60 degrees. So, what does this mean? The sum of these two should be 30 degrees and it is up to us to apportion the 30 degrees between these two, we can have a large space like due to the 0 or the pole, but the sum of them has to be 30 degrees.

Now, if you make one of them very large, the other one has to be made very small and that is usually very difficult and also you see that the phase lag due to the 0 depends only on the ratio Gm 1 by Gm 2; clearly to make this small you have to make Gm 2 much more than Gm 1 this is very clear right that guideline appears directly from this. Gm 2 has to be more than Gm 1 by a significant factor because if Gm 2 are equal to Gm 1, this would be 45 degrees and there is no way to make this 30 degrees ok. In fact, we have to keep this number well below 30 degrees right.

So, let us say for instance we will take Gm 2 equals 4 times Gm 1. Then, this particular number will be tan inverse 1 by 4 which is approximately 14 degrees ok. So, this sounds

like a reasonable choice. Then, we have 14 degrees from this and again I have 16 degrees from there; we will have 16 degrees for this one and we have to adjust the value of P 2.

So, that this number happens to be 16 degrees. This in essence is their design of the opamp or this level ok; we have not yet gone to the transistor level. There is a reason we discuss the opamp at the level of the control sources before going onto transistor level. So, that these issues with transfer function and loop gain and so on come out very clearly without being distracted by the transistor level details ok.

So, what do we do when we have to design a two stage opamp? We have to choose the second stage trans conductance. So, Gm much more than the first stage Gm let us say we make it 4 times again not a sacred number you could choose 3, you could choose 6 whatever is convenient. If we do choose 4, the 0 will give a 14 degree phase lag and you will have 16 degree phase like left for the second pole and you can adjust the second pole. So, that you get only 16 degrees phase like from that ok.

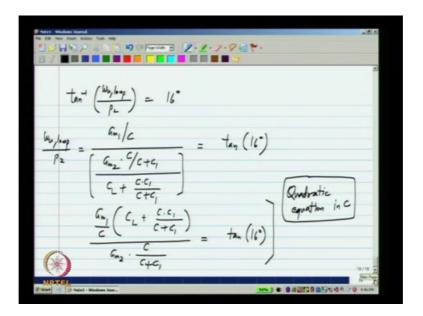

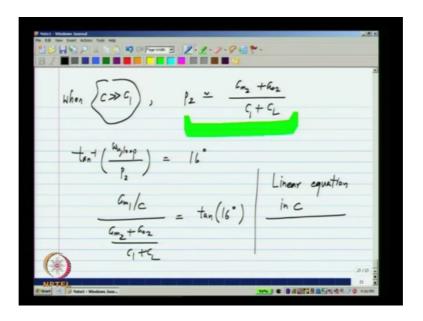

(Refer Slide Time: 37:58)

Now, what does this give you first of all omega u loop itself is Gm 1 by C and P 2 is Gm 2 C by C plus C 1 divided by CL plus C C 1 by C plus C 1 ok. And this is the ratio omega u loop by P 2 and that is tan 16 degrees ok. I have here neglected the contribution due to Go 2 because that is expected to be much smaller than the contribution due to Gm 2 right.

Now I will expand this out, I will get equals tan 16 degrees. Now, what comes out of this is a quadratic equation in C ok. So, given CL and C 1 and the values of Gm 1 and Gm 2 you can solve for this ok.

So, let us try to put it in a more illuminating form.

(Refer Slide Time: 39:53).

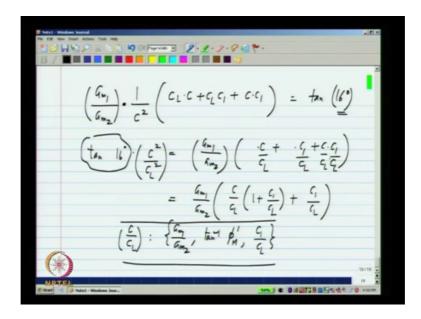

We will have Gm 1 by Gm 2 times 1 or C square appears there and the 16 degrees can because we chose G m 2 by Gm 1 of 4, otherwise we would get some other number ok. Now, I will divide both sides by CL square; it makes sense to express everything as a fraction of the load ok. So, here I will get C by CL and here I will get C 1 by CL and here I get C by CL times C 1 by CL.

So, that is what this whole thing is. So, this is a quadratic equation in C by CL square and it intuitively makes sense to normalize everything to CL because if you have a large CL; then, that means, that the unity gain frequency of the second opamp that we used to make the current controlled voltage source tends to be small and we already said that the unity gain frequency of the overall opamp has to be smaller than that unity loop gain frequency of the second loop; otherwise the second loop is not behaving like an ideal feedback loop.

So, that means, that we will have to have a large C or a small omega u ok. So, if you have a large load capacitance all the other capacitance also tends to be larger ok.

So, you can calculate C by CL from this expression based on the ratio Gm 1 by Gm 2; the phase margin that we have I will put phi m prime because this is the phase lag excluding the phase lag due to the 0 and it also depends on this ratio C 1 by CL ok. So, the bottom line is it can be calculated based on these things and then, you can verify it with simulation whether it is exactly right or not ok. So, let us go back here, we have the expression for the poles and the 0.

(Refer Slide Time: 43:38)

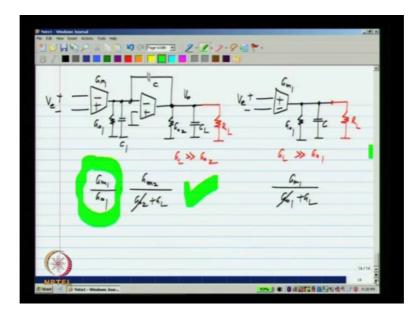

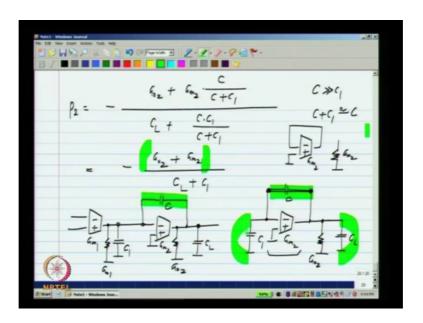

Now, in certain conditions the expression for this pole can be further simplified ok, this P 2. Now, what is the expression for P 2? It is minus Go 2 plus Gm 2 C by C plus C 1 divided by CL plus C C 1 by C plus C 1 ok.

Now, let us imagine a case where C is much more than C 1. Let us say the design values turn out to be like that ok. So, what does it mean? I will approximate C plus C 1 by C itself. So, P 2 becomes minus Go 2 plus Gm 2 divided by CL plus by CL sorry minus Go 2 plus Gm 2 divided by CL ok.

Now, does this make intuitive sense? Again, let us go back to the structure that we have ok. Now, what we are assuming is that this C the capacity of C here is much more than the capacitor C 1 over there ok.

So, what does it mean? Earlier, we assume that in this feedback, we had a division ratio of C by C plus C 1. Now, if C is much more than C 1, there is no division at all. Any

voltage that appears here also appears there ok. So, C is approximately like a short circuit right. In that case we will have this topology, when this is a short circuit I just shot this. Now, if this Gm 2 is shorted on itself ok, the conductance is nothing but Gm 2 itself ok. So, if we have Gm 2 like that it looks like a conductance whose value is Gm 2 or a resistance of 1 over Gm 2.

So, the total conductance is Gm 2 plus Go 2 that is what we see here and there is a mistake in the denominator here it should be CL plus C 1 ok. Clearly you see that if C is very large, what happens is you will simply end up with C 1 here and we have these 2 capacitors C 1 and CL in parallel. So, we have Go 2 and Gm 2 in parallel with CL and C 1 and the second pole expression becomes C 1 simpler than before; it is simply Gm 2 plus Go 2 divided by C 1 plus CL ok.

(Refer Slide Time: 47:00)

Now, this is true only when C is much more than C 1 which may or may not be true always ok, but what you can do is use this expression for P 2 as a first cut approximation ok.

Now, that is useful because we earlier said tan inverse omega you loop divided by P 2 should be 16 degrees or some particular value that we this to have ok. Now, omega you loop is Gm 1 by C and P 2 is Gm 2 plus Go 2 divided by C 1 plus CL ok. So, now, you see that we have linear equation in C it is much easier to solve.

So, what you can do is you can use this further approximation for the value of P 2 and get a first cut value of C based on the linear equation solution which is very easy to compute. Sometimes when you are calculating things in your head this may be the method to follow and finally, you can see really whether C is much more than C 1 or not. Now, if C terms out to be much more than C 1, you do not have to do anything further. If C is not much more than C 1, what you will have to do is to go back and recalculate based on the quadratic equation ok.

(Refer Slide Time: 48:51)

Thank you; I will see you in the next class.