## Digital Integrated Circuits Dr.Amitava Dasgupta Department of Electrical Engineering Indian Institute of Technology, Madras Lecture-8 Qualitative discussion on TTL Circuits

So up to now we have gone through some of the BJT models and as well as we have studied in detail the BJT inverter circuit and now we are in a position to start on the different bipolar logic families and see how this inverter circuit together with some additional circuitry give rise to the different logic families. We shall in fact take up the TTL gate first and see how it actually evolved. Now for that first let us look at this circuit which consists of resistance power supply and two diodes. So if you call this input A input B the two inputs and the output Y and I say that this is a logic circuit that is the output Y is a Boolean function of logic inputs A and B. Now what is the logic which you derive from this circuit?

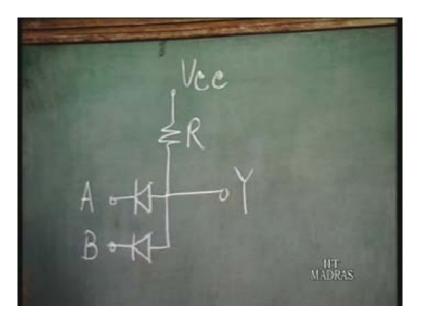

(Refer Slide Time 2:24)

You have to look at it this way that is suppose if both the inputs are low, what is the state of the output? It is going to be low. Suppose one input is low and one input is high what is the output? It is still going to be low because if this is low say there is a conduction here, suppose if A is low this particular diode is going to conduct the current is going to flow and this point is also going to be low. Now suppose if both the inputs are high then what is the state of the output? Say output is also going to be high because this input is high that means there is going to be very little conduction here. Suppose this v.cc is 5 volts, if you also apply 5 volts here these diodes cannot conduct and there is no current flowing here so this output is also going to be 5 volts. What gate

is it? It is going to be a AND gate because only when both the inputs are high the output is high, when A and B is high then only the output is high. For all other cases the output is low.

Now you know that with an AND gate you cannot realize all logic functions, so usually in a logic family the standard or basic gate of a logic family is usually what are called the universal logic gates. The universal logic gate is a gate with which you can realize any Boolean function. Now what are these universal logic gates? They are either the NAND gate or the NOR gate. The basic gate is either a NAND gate or a NOR gate. Now how do you convert this AND gate to a NAND gate? You have to follow it up with an inverter.

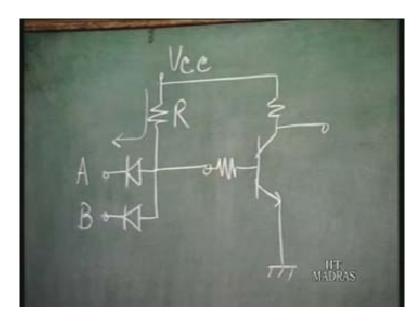

(Refer Slide Time 5:00)

We are aware of what is an inverter circuit. So we will add an inverter here, a wellknown inverter circuit and take the output here, so this should give us a NAND gate because we had a AND function here and we have a NAND, we have a inverter here so this should give us a NAND gate, but does it really work that is what now we have to see. Whether this circuit is really going to be functional? The question is when this input is low, when any of this input is low the output should be high because this is a NAND gate which means that when any input is low the output transistor should be cut off. So we have to ensure that when any input is low the output is cut off.

Now suppose the input low usually for a logic gate on a BJT, we usually take it as 0.2 volts because that is the voltage of a saturated transistor, the collector emitter voltage of a saturated transistor. Suppose we have a 0.2 volt here, this can be anything 0.2 or 0.5 it doesn't matter really. Now if this is 0.2 volts and there is a current flowing, current will flow through this path and there is going to be a drop across this diode, when this diode conducts. Suppose we assume that this diode has a drop of 0.7 volts when it is

conducting so what is the voltage at this point here? 0.9 volts. So this voltage is 0.9 volts. Now if you have a 0.9 volt here, we have seen the BJT inverter characteristics, if this is a 0.9 volt here what happens to this transistor? This transistor is going to be in saturation but what we actually want is that this transistor should be cut off.

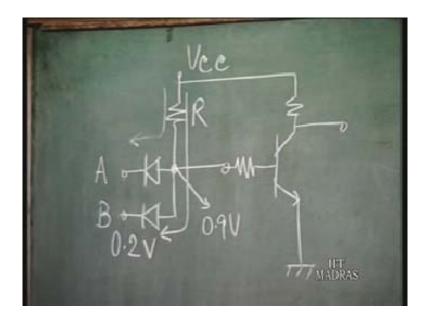

(Refer Slide Time 7:18)

When any input is low this transistor is cut off. So although it looks nice and followed by an inverter NAND but it is actually not going to work. So how do you modify this circuit in order that it is going to work? Small modification is needed. Suppose we replace this resistance here with a diode, now I am going to replace this resistance with a diode. Here I remove this resistance and I put a diode. Now this voltage is 0.9 volts here, then what happens is this 0.9 volts is going to be dropped across this diode as well as this base emitter junction and considering that the base emitter junction is also a p n junction, these diodes are quite similar, base emitter junction diode you can say as well as this external diode.

Let us say that this 0.9 volt is going to share equally between these two. So the drop is going to be 0.45 volts across each and let us say for this diode to conduct you require at least 0.6 volts. There is going to be no conduction, there is going to be no base current this transistor is going to be cut off. So this circuit will work as a NAND gate because when this input is low 0.2 volts then here is 0.9 volts, this transistor is off. Now when you raise this input what actually happens this voltage is also going to get raised and suppose when this voltage goes to 1.2 volts say then you have 0.6 volts across this each of them and when it goes even above that then it starts conducting, the transistor turns on, the output voltage is going to fall.

So when the input goes high, what is going to happen if this input is sufficiently high, even if this input goes to five volts, you have the current flowing here. This transistor is going to turn on, output is going to be low. So this circuit actually behaves like a NAND gate. Although one must say that this characteristics is not good but will not go into the details of this but this circuit again has a very serious problem. The problem with this circuit is related to its switching circuits. I am just giving a hint, it is related to the switching properties that is we have seen the switching of a bipolar transistor.

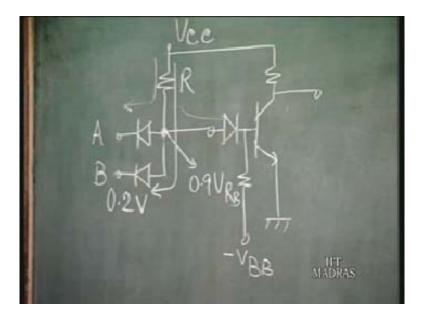

Now if you want to switch off a bipolar transistor what do you require? When the transistor is to be switched off you have to remove say when this transistor goes from saturation to cut off you have to remove the excess stored charge in the base. Now how do you remove this? This base charge has to be removed by a reverse base current. Now this removal of this reverse base current is very important in switching of a bipolar transistor, otherwise it will take a long time. So you require a reverse base current. Is there a mechanism for providing reverse base current? There is no mechanism for providing a reverse base current. So it will take a long time to switch off. Now what can be done is some modifications provide the resistance like this, so there is a negative supply voltage provided, we have a base resistance like this.

(Refer Slide Time 11:33)

So normally what is going to happen? A current flows in, turns it on but when this when this input goes low this voltage is low then this is say around 0.7 volts, this is a negative voltage a reverse current flows this way to switch off the transistor but this is not a good solution from two points of view. One is that you require a negative power supply which is not a good thing because you have to have a dual power supply which is not convenient for any circuit engineer. Number two if you put a resistance like this, when the transistor is switching on the current has to flow into the base and the part of

the current actually gets diverted here. So the entire current does not flow into the base and so it slows the device.

In order to switch on the transistor, you require a sufficiently large we have already seen that on time of a transistor that is you require a sufficient large base current flowing into the base of the transistor but this is going to divert some current. So this is not a good solution but this is one of the earliest logic families, basic circuit of the earliest logic families called the diode transistor logic, this circuit DTL diode transistor logic but this has the drawbacks which i just mentioned. It is a very slow circuit because of these problems associated with switching.

Now the TTL or the transistor transistor logic is actually derived from this circuit. Now if you look at this structure here, the two diodes here and this diode here, now this particular structure can be replaced by what is called a multi emitter transistor. I will just come to that what is the multi emitter transistor. This is nothing but you know similar to this, you have two p n junctions this way and one p n junction this way. So this is 2 p n junctions but this is a transistor structure basically. This is called a multi emitter transistor and then if you have the same thing, so actually it is the same circuit we have replaced these three diodes with a multi emitter transistor.

Now these are the inputs here and this is the output point, exactly the same circuit. Now what is a multi-emitter transistor? I will just tell you, draw the figure of a multi emitter transistor. You are familiar with this, it's a normal transistor structure by now I suppose.

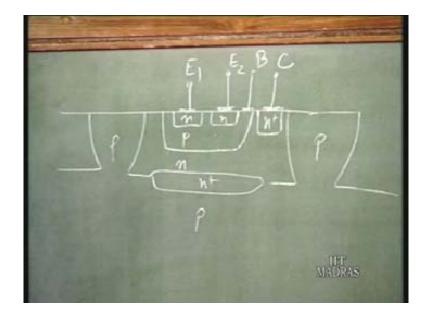

So this is the base then normally you have one emitter suppose you have two emitters like this. So say this is emitter one contact, we have a second emitter contact here, I take the base contact here in this region. This is the collector so this is n p n, n p n, this is n plus. Of course you have the buried layer here also, this is p p.

(Refer Slide Time 16:26)

This is the structure cross sectional structure of a multi emitter transistor, you see the difference between the normal transistor and the multi emitter transistor is that instead of one emitter you have two emitters. So basically it is like, this is one transistor this is another transistor. There are two transistors with a common collector base junction. So this is the collector base junction, this is common to both the transistor and you have two emitter in the base. So if you look at the top view, I will just draw the top view also for you. This is the base, this is the collector diffusion n plus and you have the collector contact here, you have the base contact here and then you have two emitters and these are the two emitter contacts. So this is  $E_1$  emitter one this is emitter two, this is the base, this is the top view looking from the top and this is isolation region which the transistor is raised.

So this is the multi emitter transistor, basically again just to repeat a multi emitter transistor is a transistor with a common collector base junction but separate emitter base junction. So you can consider them as transistors in parallel or less such. There is a space saving, if you have a multi emitter structure rather than having to fabricate two separate bipolar transistors.

(Refer Slide Time 18:29)

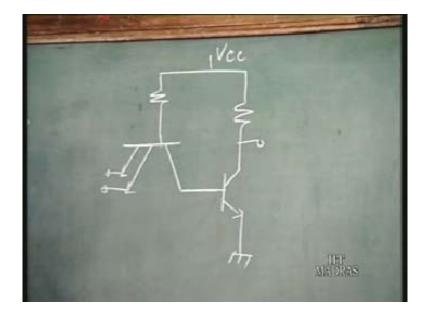

So we go back to the circuit here with a multi emitter transistor and see how this transistor actually behaves as a NAND gate. How this circuit behaves as a NAND gate? Again you have the two inputs A and B, this is the output Y. So this is one resistance, this is other resistance. Now what happens is suppose this input here goes low what happens?

So suppose this is 0.2 volts here what is this voltage going to be? Around 0.9 volts say and suppose this resistance is 4 kilo ohm and this is 5 volts. So a current 5 volts minus 0.9 volts divided by 4 kilo ohm, around one milli ampere current flows here that is the base current and this flows into the emitter, this transistor is working in the normal mode now and there is a tendency of a collector current to flow in this direction but of course a current normally cannot flow out of the base.

So this behaves as a very high resistance and this transistor which is almost a zero collector current is, in which state it is in? In saturation you can say, very high base current very small collector current. There is no current so this transistor actually gets no base current, so what is the state of this transistor? It is off, it is cut off so the output is going to be high. When any input goes low the output is high, when both the input goes high, when you raise the input what is going to happen is, you see this is the p n junction here, there is another p n junction this is p n, this is another p n, this is n p n.

(Refer Slide Time 20:37)

Vec(SV

A p n junction cannot be forward biased by more than say 0.75 or maximum 0.8 volts or so. It cannot go beyond that because of the nature of the characteristics of the p n junction. If the forward voltage goes higher than that that means there is very large current is flowing and which cannot flow because of this limiting resistance. So the voltage across this p n junction, let us assume will be around 0.7 volts or so. So this voltage here at this point cannot be more than, that is the base of this multi emitter transistor this voltage cannot be more than 1.4 volts or so. Because if it is more than 1.4 volts, it would mean than one of this p n junctions is forward biased by more than 0.7 volts or so which is not possible.

So if this voltage is 1.4 volts or so and suppose we have raised this voltage to much higher than that, that is this emitter input point what does it mean? This emitter base junction is reverse biased and what is the state of the base collector junction? Forward bias. So for this transistor it's a peculiar situation, the emitter base junction is reverse biased whereas the base collector junction is forward biased, you normally operate the transistor in the other way that is the base emitter junction is forward biased, base collector reverse biased. So it is called the reverse active mode of operation. It is working in the reverse mode of operation and when a transistor works in a reverse mode that is basically you have interchanged the emitter and collector terminals, what is the value of beta? The beta of the transistor is very small, now again you see what is happening is this voltage is around 1.4 volts now say, if this voltage is 0.4 volts this is 5 volts supply. So a current will flow into the base.

(Refer Slide Time 24:12)

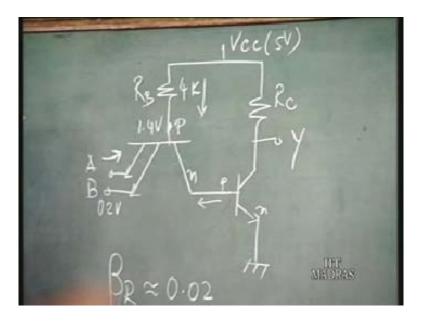

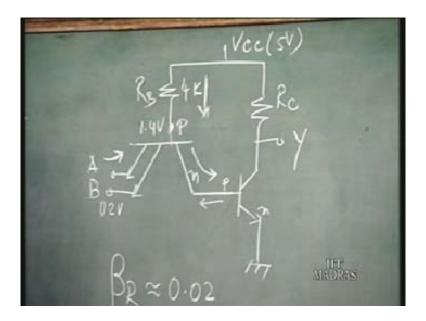

There is a base current for this transistor, now the beta of this transistor is very low, what does it mean? In fact these transistors are so designed that the beta reverse, the reverse beta of this transistor is approximately made smaller say about 0.02 or so. So it means that the collector current by the base current ratio of this transistor is going to be 0.02. So a very small current, so this is now behaving as a collector, this is behaving as the emitter if you look at it the normal operation. This current is very small and it is in the reverse mode so this is behaving as an emitter. So if the collector current is very small and you know that the emitter current is the sum of the base current and the collector current, so you can say that the emitter current is almost equal to the base current. So whatever is the current flowing here is almost the same current flows in like this and this current is quite large that is it is almost 3.6 by 4 k that is around 0.9 milli amperes and so this is about 0.9 milli amperes of base current flows into this transistor and that should be large enough to make this transistor go to saturation.

So when this input is high, this current flows into the base. Basically what is happening is if you look at it this voltage here cannot rise above a certain value. So there will always be a current flowing here into the base of this transistor, when this input is low that current flows into the input and no current flows into the base. so this transistor is starved of current so it is cut off, when this input goes high this current which is flowing into the base of this multi emitter transistor flows towards the input of this transistor and this transistor turns on and goes to saturation. (Refer Slide Time 25:26)

So this transistor goes to saturation, the output voltage goes low. So we can say when both the inputs are high, the output transistor goes to saturation and the output is low. So this behaves as a NAND gate. Now suppose this transistor is in saturation and suddenly you make this input go low, what is going to happen? This input has gone low so this transistor will go back into the normal mode of operation from the reverse mode, this becomes a 0.2 volts here. This voltage goes to 0.9 volts, the current flows into the normal mode, this junction gets forward biased, the emitter base junction gets forward biased. So there is a base current flowing in and so there will be a tendency of the collector current flowing and this collector current what is it doing?

It is removing the base stored charge of this transistor. Suppose we have seen if this is 0.2 volts and this is 0.9 volts here, the base current is 1 milli ampere, slightly more than one milli ampere and if the beta of this transistor is even conservatively to say 25, the collector current should be around 25 milli ampere, it can support a collector current of 25 milli ampere. So a large current will flow out of the base of this transistor because there is charge stored, this can support the collector current till there is charge here. So this is drawing out the base charge of this transistor and this current is going to exist as long as the base charge is there.

Once this charge has been removed so there is no voltage source here, there is no source of charge so basically this collector current is going to go to zero, this transistor goes to saturation. So you see when you compare with the DTL circuit, this is the similar situation as I said, this circuit looks similar basically you have converted three diodes into a multi emitter transistor but the advantage is the transistor action here and

this biased transistor action actually removes provides a very large current to remove the base charge of the output transistor when that transistor is to go from saturation to cut off. So that is the major advantage of this circuit.

So this is the basic TTL circuit, transistor transistor logic circuit and in fact the propagation delay of this circuit when you compare to the previous circuit here the diode transistor logic circuit is about one tenth, the propagation delay is about one tenth. So you have an order of magnitude improvement in speed from TTL to the DTL because of the improved removal of base charge storage mechanism in the TTL circuit. So this is the TTL basic transistor transistor logic circuit. So we know that this circuit now behaves as NAND gate and is much better than the previous DTL circuit but again this circuit has its share of problems or I mean everything has its problems but we have to look at ways how to improve it.

So most of the delay associated with this circuit is that is suppose this circuit is driving a capacitive load. Now when this transistor goes from saturation to cut off what is going to happen to the output voltage? The output voltage should rise from say low to high, so this point the voltage should rise from low to high. Now this is cut off, so how can this point so this capacitance when it was low the voltage across this capacitance was low. Now when this point has to rise this capacitance has to get charged, so the current must flow; normally when this is saturation the current flows into the transistor but when this goes off transistor has gone off the current flows into the capacitance charging the capacitance and the delay of this process is given by the  $R_{\rm C}$  time constant current.

(Refer Slide Time 30:38)

In order to reduce the  $R_{\rm C}$  time constant of course you cannot reduce c because that is the load, for a particular load if you want to reduce the  $R_{\rm C}$  time constant you have to

reduce the collector resistance but collector resistance if you reduce there is some problem. The problem is that when this transistor is on that is the output transistor is on, if this collector resistance is low you have a large current flowing and the power dissipation is going to be more. Also if the collector resistance is low it is difficult to drive this transistor to saturation. Isn't it? Because  $I_{Csat}$  that is going to be much higher and you require a larger base current to actually drive the transistor to saturation. So on time in fact is going to go up. So you cannot make  $R_{C}$  too low. Now basically our requirement is that when this output transistor is off, let me call this as  $T_{0}$  output transistor, when  $T_{0}$  is off we want  $R_{C}$  to be low because of the low  $R_{C}$  time constant and when  $T_{0}$  is on we want  $R_{C}$  to be high.

(Refer Slide Time 32:36)

un This OFF 111

So basically we have two conflicting requirements and you cannot achieve these two requirements with a passive resistance, with any passive element because the resistance will always have the same value, cannot change this value, it is always going to have the same value. So what you require is an active element that is a transistor for example. A transistor in its off state will behave as a very high impedance and in on state will behave as a low impedance device. So we require a circuit what is called an active pull up. This resistance is called pull up because pull up resistance because the output is actually pulled up through that resistance. So this is a pull up device and this is the pull down device because when the output has to be pulled down to lower values, this capacitance has to be discharged through this. This turns on, the capacitance discharges through this so this is the pull down device that is a pull up device.

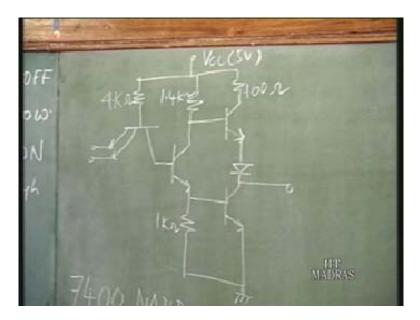

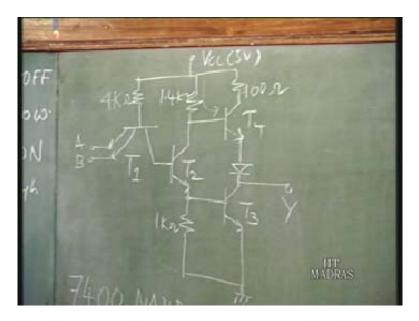

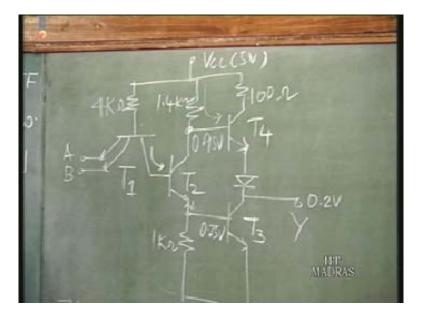

So what you require is instead of a passive pull up you require an active pull up. We understood why we require that. So now we shall again modify this circuit and go to the next stage of development. So it has developed with time in this fashion. Let's see the next circuit. So this is v.cc. 5 volts, TTL power supply voltage is 5 volts. This is the very familiar well known circuit for the 7400 that is the chip number, 7400 NAND gate. So this is 4 kilo ohm, this is 1.4 kilo ohm, this is one kilo ohm, this is 100 ohms. So this is the well-known circuit which you see that the resistance has been actually replaced. So this is the output side, this is the same input side as previously this is the output side and this is the output transistor, the pull down transistor which is still there and in the pull up side you have these many components. Now shall come to that why you require all of them.

So this is the pull up side you have replaced and you have a circuitry here consisting of one transistor and two resistances here, this is what is called the face splitter.

(Refer Slide Time 36:00)

Now the idea the purpose of this is when you have a transistor and it behaves as an amplifier, the emitter point is actually has a positive gain whereas the collector point has a negative gain. So this transistor actually achieves the purpose of, so when one of this transistor is on the other will be off. So when this is on the pull down is on, the pull up will be off pull, down is off the pull up is on. So that is what is achieved by this part so we shall again go through this circuit qualitatively. Now again just like in the previous case, these are the two inputs say this is the output. When any input goes low, this multi emitter transistor is working in the normal mode and when it works in the normal mode there is a tendency of current to flow out.

So what happens to this resistor? So let me call it this is  $t_1$ , this is  $t_2$ , you call this  $t_3$  and let me call this  $t_4$ . So what happens to  $t_2$ ?  $T_2$  goes off and when  $t_2$  is off what happens to  $t_3$ ?  $T_3$  will also be off because if  $t_2$  is off there is no way that  $t_3$  can get any base current. So because the base current of  $t_3$  could only be supplied by the emitter current of  $t_2$ . So  $t_2$  is off,  $t_3$  is off. What about  $t_4$ ? It is on because its base is connected

by a resistance to the power supply so it is going to get sufficient base current, base current is going to flow into t<sub>4</sub>.

(Refer Slide Time 38:05)

This transistor  $t_4$  turns on and when this transistor turns on, this provides a low resistance and connection to the output. So we shall see what exact values and all. So this transistor turns on, so when  $t_3$  is off,  $t_4$  is on and the resistance seen at this output end is actually the base resistance divided by beta of this transistor. You know that how you reflect the base resistance on to the emitter side. So that is going to be a low resistance. We look at the other situation, what happens when the input goes high? When the inputs go high rather then what is the state of this transistor, it is acting in the inverse mode. So the current which flows here is going to be a large emitter current flowing and of course a part of it goes here but major portion flows into the base of  $t_3$  because emitter current is beta times the base current.

So there is a large emitter current here, so  $t_3$  will get very large sufficiently large base current to turn it on, go to saturation in fact. What happens to  $t_4$  that is what we have to see now? Suppose  $t_3$  goes to saturation then what is this voltage at the output low, say 0.2 volts and the voltage at the base here, suppose we assume this to be around 0.75

volts say that is the base of transistor t<sub>3</sub>. Now this t<sub>2</sub> let us assume this has gone to saturation, now what is the voltage at the collector of t<sub>2</sub> in that case? 0.75 + 0.2, so it is going to be 0.95 volts.

(Refer Slide Time 40:46)

So you have a drop of 0.75 volts between the base of t4 and the collector of t3. So you have a 0.75 drop shared between the base emitter of t4 and this diode here. This actually explains why we require a diode here. If the diode was not present here, this transistor would never have gone off but now this 0.75 volts is shared between these 2 p n junctions. So neither of the p n junctions can turn on. So this is going to be off so basically at the collector of this transistor t3 you see a very high resistance. So we have achieved what we have set out for. That is when t3 is off, we see it is a very low resistance because t4 is on and when t3 is on, this goes to saturation, you have a very high resistance working here, so you have very low collector current flowing. So this is the basic TTL circuit, 7400 NAND gate which was available commercially in the mid-sixties, one of the earliest versions of the TTL gate.

So the next thing what we should do is now we should go into it a little more quantitatively in order to understand the working of the circuit that is where input output voltage how it looks like, the characteristics of the circuit. we shall take it up in the next class because we don't have sufficient time for going through this class that is what is the nature of the input output characteristics, we shall study that then we shall look into further modifications. This is the first early version of TTL, the TTL gates which are available nowadays have been further modified many number of times. So we shall see again, so this has its drawbacks and further modifications how they improve their properties. So in fact just to tell you that this particular NAND gate had a power dissipation of a 10 milli watts and a propagation delay of 10 nano seconds. This power dissipation obtained milli watts per gate and a propagation delay of ten nano seconds. So we shall go ahead with this in the next class and we shall see how exactly as we go along and see further improvements how these properties have been improved upon.

(Conversation between professor and a student: sir how that phase splitter will work so that one of the  $t_4$  or  $t_3$  only turn on) basically we have discussed that qualitatively, quantitatively we will see in the next class. What happens is when this input is changing, this circuit behaves as an amplifier and this amplifier has a gain, if you have collector resistance of 1.4 k and emitter resistance of one k that the collector point is a gain of minus 1.4. So basically what is happening is when this input is rising, this emitter voltage is going to rise but the collector voltage is going to go down.

So when this emitter voltage rises it turns on t<sub>3</sub>, whereas it cuts off t<sub>4</sub> because of the negative gain in the collector point whereas when you look at it the other way that is when the input voltage is reducing this t<sub>3</sub> is cut off and the t<sub>4</sub> goes into conduction. So basically we have already seen sort of that when t<sub>3</sub> is on t<sub>4</sub> will be off and when t<sub>3</sub> is off, t<sub>4</sub> will be on. Next class we shall see it more quantitatively, we shall put down values and see at what input voltage is exactly these transitions take place that is one transistor going off and the other turning on and so forth. That is we are going to do it more quantitatively, so that we can actually derive the exact input output characteristics of this gate which is important because that will also help us to understand I mean what further modifications are required to improve the input output characteristics. So that would give us an idea of the next generation of TTL gates of how they are developed, what modifications are done and so on.