## Digital Integrated Circuits Dr. Amitava Dasgupta Dept. Of Electrical Engineering Indian Institute of Technology, Madras Lecture – 14

## I2L Condition for Proper Operation; Noise Margin

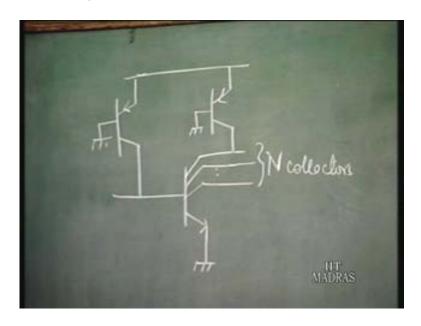

So we shall continue our discussion on looking at the conditions for proper operation of the I squared L cell. That is how to ensure that the NPN transistor in an I squared L cell actually goes to saturation because as we had seen the condition of the PNP transistor at the base that is the current source, this PNP transistor is actually in saturation and so it has to be ensured that the base of this NPN transistor gets sufficient current in order to drive this transistor to saturation. So we had started that discussion and so this is the I squared L cell and this is the transistor with say n collectors, n is any number.

(Refer Slide Time 02:25 min)

As we had said that we will assume that this multi collector transistor having n collectors is actually n transistors in parallel. That is the base and emitter are in parallel, the bases are all shorted, emitters are all grounded and they just have separate collectors. So basically they are n transistors and the transistor parameters which will talk of like IS the Ebers-Moll model refers to each individual transistor. IS, when we say is actually the saturation current for one of these transistor. So again the model which we will be using is the Ebers-Moll model, I will just draw it once more. So you have three current sources and this is the collector, this is the base, this is the emitter. So this current source is Is by betar exponential V<sub>BC</sub> by V<sub>L</sub> minus one and this is Is exponential V<sub>BE</sub> by V<sub>L</sub> minus exponential V<sub>BC</sub> by V<sub>L</sub>.

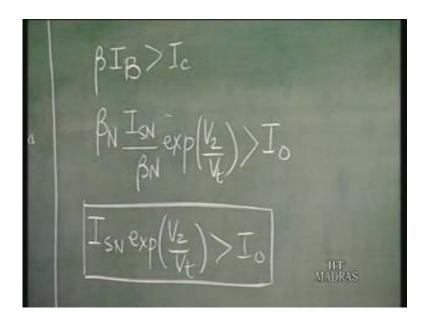

So in this model we will try to derive a condition for the values of these parameters of the individual transistor that is Is and beta of the NPN and PNP which must be satisfied so that this cell works. That is this transistor NPN transistor goes to saturation. Now the condition for saturation we know is that when the base current, the beta times Is is greater than Ic. So if you consider them as n transistors, so the total collector current for the n transistors is n Io, so this is beta, I write N here to differentiate between the beta of the forward and the reverse. Betan Isn so base current of the NPN transistor, if we go back again to this model, the base current is given by the sum of these two current sources. Now assuming that VBC is less than VB, although the transistors actually is in saturation but when it is just going into saturation, VBE is much greater than VBC. May not be very much later but because of the exponential relation, if this VBE is 0.7 VBC is 0.5, 0.7 by V1 exponential is going to be much greater than "point five" by Vt exponential because of the exponential nature.

(Refer Slide Time 05:57 min)

So we can neglect this part and we can just take exponential V<sub>BE</sub> by V<sub>L</sub>. Here what I will do is again I just write this voltage here, I call this voltage V<sub>2</sub> and I call this voltage at this point V<sub>L</sub>. Of course this is coming from some external region but this voltage is V<sub>L</sub> and this voltage here as V<sub>2</sub>. So this becomes exponential V<sub>2</sub> by V<sub>L</sub>, so this is for one transistor and this must be greater than I<sub>0</sub> where I<sub>0</sub> is the current flowing in here. Now here I call this I<sub>0</sub> (Refer Slide Time: 07:08). So the condition for saturation is I<sub>SN</sub> exponential V<sub>2</sub> by V<sub>L</sub> must be greater than I<sub>0</sub>, so this condition must be satisfied.

(Refer Slide Time 07:29 min)

So of course if you have n transistors, the total collector current is going to be n times this and here you have to consider n times the total base current which is n times given by this expression. Now what is Io? It is the current for this PNP transistor. Now for the PNP transistor, the base emitter voltage is going to be around 0.7 volts of that order whereas the base collector voltage, this transistor is in saturation we are looking at the condition for saturation. The base collector voltage is around 0.2 volts. The base collector voltage is much less than the base emitter voltage. When we look at the PNP transistor so it is in the active region, this PNP transistor. I call this P2 and let me call this P1, so P2 is in active region and so here we can say VBC for the P2 transistor is much less than VBE, the base collector voltage is much less than VBE.

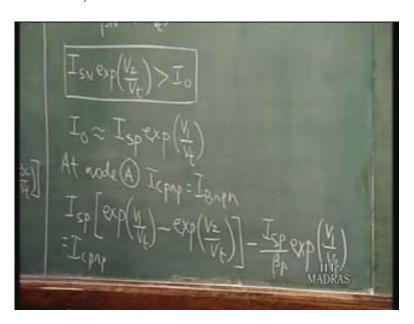

So the collector current can be expressed as,  $I_{0}$  can be expressed as; so this is going to dominate, all the  $V_{BC}$  terms as small. So you can say that  $I_{SP}$  stands for the  $I_{S}$  of the PNP transistor, exponential  $V_{BE}$  by  $V_{t}$  for the PNP. So what is that voltage?  $V_{L}$ , of course  $V_{BE}$  is minus  $V_{L}$  but see that the current detection are changed. I mean we can write in terms of  $V_{L}$  by  $V_{L}$ . So  $I_{0}$  is  $I_{SP}$  exponential  $V_{L}$  by  $V_{L}$ , so this  $I_{0}$  value is given by this. We have to see that this condition is satisfied.

Now at this point the next thing what we do is we write an equation of the current at this point. So when this transistor goes to saturation it means that all the transistors whose collectors are connected at this point are cut off. So whatever collector current is flowing for this PNP, that is P one flows in as base current of the NPN transistor. So we can write an expression, I will

call this node A at collector current IC of PNP is equal to I<sub>B</sub> of NPN. So what is the collector current of PNP given by? Again we go to the Ebers-Moll equation, collector current is this current source minus this current source so I write I<sub>SP</sub> exponential V<sub>BE</sub>, V<sub>BE</sub> of the PNP is again V<sub>L</sub>; V<sub>L</sub> by V<sub>L</sub> minus exponential V<sub>BC</sub> by V<sub>L</sub> which is with exponential V<sub>L</sub> by V<sub>L</sub> minus this current source.

So I<sub>SP</sub> by beta P that is the beta of the PNP transistor, actually this should be the reverse beta of the PNP transistor but since the PNP transistor is lateral transistor, it is not a vertical transistor. It's a lateral transistor with the two emitters and collectors side by side, the reverse and forward betas are almost the same. So we can take it as beta P which is the beta of the PNP transistor. So I<sub>SP</sub> beta P exponential the base collector voltage; base collector voltage of the PNP is again V<sub>1</sub>.

(Refer Slide Time 13:03 min)

So this is the collector current of the PNP transistor and this has to be equated to the base current of the NPN transistor. So what is the base current of the NPN transistor? So this is I<sub>Cpnp</sub>, I<sub>Bnpn</sub> is going to be equal to again the base current is the sum of these two current sources, for the PNP. So we have already taken that so I<sub>SN</sub>, so there is n times total base current I<sub>SN</sub> by beta N exponential V<sub>2</sub> by V<sub>4</sub>. So what do you get now? So we have to equate these two equations, the I<sub>Cpnp</sub> with I<sub>Bnpn</sub> and then we have to get the condition for saturation. Now once we equate that we can write it this way. The equation now what you get finally, you can write it as I<sub>SP</sub> exponential V<sub>2</sub> by V<sub>4</sub> is equal to I<sub>SP</sub> exponential V<sub>4</sub> by V<sub>4</sub> minus, so this is equal to this thing. I think there is some mistakes somewhere. At node A, ISP exponential V<sub>4</sub> V<sub>4</sub> minus exponential V<sub>2</sub> by V<sub>4</sub> minus V<sub>BC</sub> this one is the mistake I think (Refer Slide Time: 16:28). This has to be minus exponential, this is for the PNP, this is base collector, this is V<sub>2</sub> we made the mistake here.

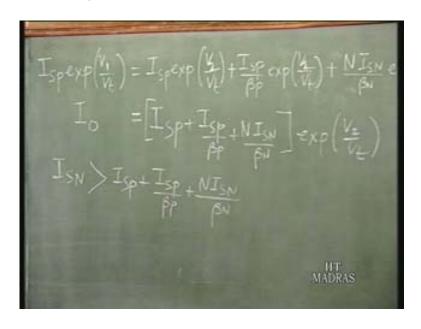

So this is  $I_{SP}$  by beta<sub>P</sub> for the PNP, just we go back here.  $I_{SP}$  exponential  $V_{BE}$  by  $V_{t}$  minus  $V_{BC}$  by  $V_{t}$ . So exponential  $V_{L}$  by  $V_{t}$  minus  $V_{L}$  by  $V_{t}$  minus  $V_{L}$  by beta<sub>R</sub> exponential  $V_{BC}$  by  $V_{t}$ . So for the PNP,  $V_{BC}$  is  $V_{L}$ , so this has to be  $V_{L}$ . So this is going to be equated with this (Refer Slide Time: 17:19). So now I think I just rewrite this, this becomes  $I_{SP}$  exponential  $V_{L}$  by  $V_{t}$  equals  $I_{SP}$  exponential  $V_{L}$  by  $V_{t}$  plus  $I_{SP}$  by beta<sub>P</sub> exponential  $V_{L}$  by  $V_{t}$  plus  $V_{L}$  so this is equal to, I can write  $V_{L}$  by beta<sub>P</sub> plus  $V_{L}$  by beta<sub>P</sub> plus  $V_{L}$  by beta<sub>P</sub> exponential  $V_{L}$  by  $V_{L}$ . Now  $V_{L}$  by  $V_{L}$  has  $V_{L}$  by  $V_{L}$ , what is that?

That is the same as I<sub>0</sub>. Isn't it? ISP exponential V<sub>1</sub> by V<sub>t</sub> is given by I<sub>0</sub>, we have already derived that. So this term which we have here is actually equal to I<sub>0</sub>. So I can write here this ISP exponential V<sub>1</sub> by V<sub>t</sub> is actually I<sub>0</sub>, the left hand side is equal to I<sub>0</sub>, so I<sub>0</sub> is equal to this expression. Now again coming back here, the condition for saturation is that I<sub>SN</sub> exponential V<sub>2</sub> by V<sub>t</sub> which must be greater than I<sub>0</sub>. So I<sub>SN</sub> exponential V<sub>2</sub> by V<sub>t</sub> must be greater than that which is again some term into exponential V<sub>2</sub> by Vt. So what can I write? I<sub>SN</sub> must be greater than, so you see that we have removed all the voltage dependencies which is very important.

(Refer Slide Time 20:12 min)

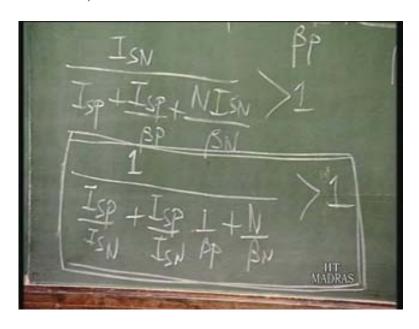

So now we have a relation between the different saturation currents, the number of collectors and the beta of the individual transistors. So I<sub>SN</sub> must be greater than I<sub>SP</sub> plus I<sub>SP</sub> by beta<sub>P</sub> plus N I<sub>SN</sub> by beta<sub>N</sub>. So this condition must be satisfied in order to ensure that the transistors goes to saturation. Now you just do some small manipulation. We can write like this, I<sub>SN</sub> must be greater than I<sub>SP</sub> plus I<sub>SP</sub> by beta<sub>P</sub> must be greater than one. Basically this divided by this must be greater than one or you can write one by I<sub>SP</sub> by I<sub>SN</sub> plus I<sub>SP</sub> by I<sub>SN</sub> into one by beta<sub>P</sub> plus N times N by beta<sub>N</sub> must be greater than one. So this condition must be satisfied.

(Refer Slide Time 22:04 min)

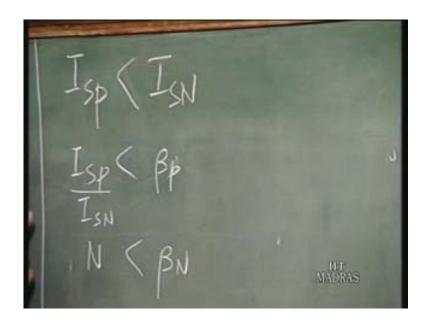

So when you say that this has to be greater than one what does it tell you about the denominator? This denominator must be less than one. Now this denominator consists of three terms so if this A plus B plus C has to be less than one, each individually has to be less than one. So Isp. must be less than Isp. So some conditions we can write down straight away. Isp. must be less than Isp. then what we can say about beta P? So again this must be less than one, so Isp. must be less than beta p times Isp. or we can write like this, Isp. by Isp. must be less than beta. Also N must be less than betan.

(Refer Slide Time 23:43 min)

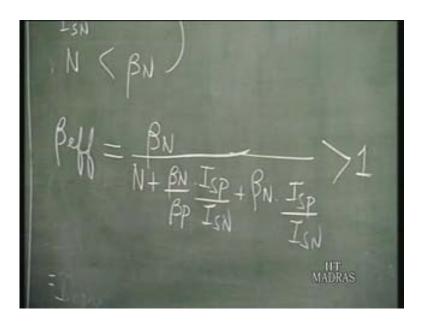

So these conditions must be satisfied but one must be careful that these are necessary conditions but they are not sufficient. In the sense that if this ensures that each of these individual terms in the denominator is less than one but if each of these terms is less than one it doesn't mean that this is going to be greater than one. So these are necessary conditions which must be satisfied but these are not sufficient conditions. So make them as small as possible. Another term which is very often used, so this condition must be satisfied. Another way of writing that expression is one term is called the beta effective is equal to betan. So if you multiply both the numerator and denominator by betan that expression there, you have betan by N plus betan by betan by Isp. by Isp. plus betan N Isp. by Isn.

This must be greater than one. This is called the beta effective, this term. The same, this here in this expression which we have shows that this fraction must be greater than one. Multiply the numerator and denominator by betan on the left hand side so it's greater than. So this term, you write like this. This is betan divided by where betan is actual beta of the NPN transistor but this is the effective beta of the I squared L cell. That is if you consider that in this cell which we go back to the cell that is if this current source is equal to this current source and then if you have an NPN transistor, if the beta is greater than one the transistor should go to saturation. That is if the collector current is the same as the base current and then the condition for saturation is the beta must be greater than one.

So this is the effective beta because from the same point, you are having two PNP transistors here. So just because of this configuration here and because of the condition of this transistor, normally if both the transistors were identically biased, these two transistors you could have equal currents and then this transistor would go to saturation if the beta is greater than one. So now what you have is an effective beta because of the different states of this two PNP transistor P<sub>1</sub> and P<sub>2</sub>. So the effective beta must be greater than one. So the beta is modified as such, if you consider it as a cell instead of a transistor, effective beta of the cell so beta<sub>N</sub> by N it's quite obvious because you have N collectors, the collector current is N times.

Again if you have same current source as Io, the collector current would be N times Io and this one would be Io, beta has to be greater than N for the transistors to go to saturation. So this N is coming because of the large number of collectors and the remaining terms in this beta effective expression is coming because of the fact that the PNP transistors at the base that actually going to saturation which means that the current source at the collector and the base they are different values. They are not the same values.

(Refer Slide Time 28:38 min)

So this is effectively modifying that expression. So this is the beta effective of I squared L cell and this is the figure of merit for any I squared L cell and the larger this value, of course it is better and this must be greater than one for the transistor to go to saturation. This also tells us from this expression, we can also calculate the different values of the different parameters that is required for proper operation of the circuit. For example I just give a small problems say, suppose you design such that Isp. by Isn is equal to 0.2 and betap is equal to 0.25 and N is equal to 4 say that is it has 4 collectors. So what is the value of betan if necessary? You can simply plug in the values in this expression and solve for betan and it comes out that of course

it's not a very large value betan must be greater than 6. So this gives us the way of finding out the individual conditions for the transistors to operate properly.

This also tells us that one must do a proper design of the I squared L cell in order to ensure that the transistor is working. That is if you just connect the transistors in that fashion, it's not going to work. For example you see that, if you look at this expression I<sub>SP</sub> must be less than I<sub>SN</sub>.

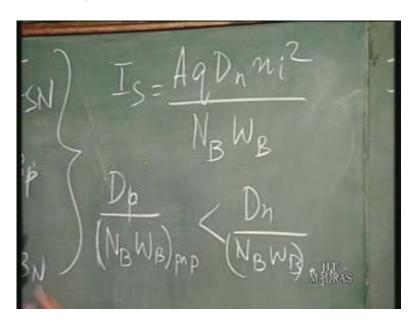

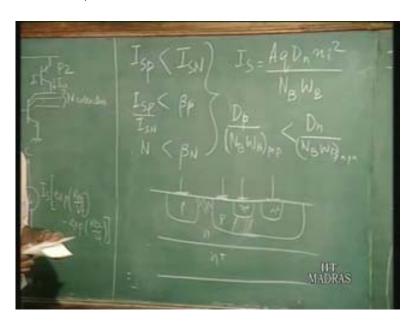

Now what is the expression for Is of the saturation current? Is in a transistor is given by, if you remember AqD<sub>n</sub> n<sub>i</sub> squared by N that is the base doping, I will write N<sub>B</sub> into W<sub>B</sub>. Isp must be less than Isn, so what you have to do is you have to ensure that D<sub>n</sub> Isp so D<sub>p</sub> by Aq n<sub>i</sub> squared they are constants, D<sub>p</sub> by N<sub>B</sub> W<sub>B</sub> of the PNP must be less than D<sub>n</sub> times N<sub>B</sub> W<sub>B</sub> of the NPN. Now D<sub>p</sub> and D<sub>n</sub>, of course D<sub>p</sub> is less than D<sub>n</sub> that is the diffusion coefficient of holes is less than that of electrons because of the mobility difference. So basically what we have to do is you have to ensure that this denominator which is, this is the base concentration and in the base width. So this actually means the total base dopants per centimeter square which is sometimes called by the (Not Understandable) number of the base or so. This expression on the left hand side has to be less than that on the right hand side, so this number for the NPN must be less, N<sub>B</sub> W<sub>B</sub> for NPN must be less than that of N<sub>B</sub> W<sub>B</sub> for PNP.

(Refer Slide Time 32:52 min)

So that this term on the right hand side is much greater than the term on the left hand side. Now if you look back at the I squared L cell configuration, I just draw it again. So these are the different collectors, this is the N<sub>1</sub>. N plus wafer so this is P, P, n plus, n plus and so this is the injector, this is the base contact and these are the collector contact.

So the base for the NPN is this region and the base for the PNP is this region (Refer Slide Time: 33:44), base concentration. So the base concentration of the PNP is this N, the substrate concentration and the base concentration for the NPN because your diffusing into the substrate, the base concentration of the NPN obviously going to be higher than that of the PNP. N<sub>B</sub> for the NPN obviously it's going to be higher than the PNP because you are diffusing, you are creating that base of the NPN by diffusing into that substrate.

So again if you look back into this condition, for the NPN the doping concentration is higher which means that this term becomes smaller which is going to create problems. So what you have to do is W<sub>B</sub> of the NPN must be made much smaller than the W<sub>B</sub> of the PNP. That is the base width of the NPN must be made much smaller than the base width of the PNP.

(Refer Slide Time 35:07 min)

So that this term N<sub>B</sub> W<sub>B</sub> the product term is much less but at the same time, you cannot make the base width of the PNP very large because again you have a condition, here you see. If you make the base width of the PNP very large, the beta of the transistor is going to fall. Again

you have a condition that this Isp. by Isn must be less than betap so again betap must be also sufficiently large. So you see that there are lot of interdependencies for the different conditions which must be satisfied in order to ensure that the I squared L cell works. So just wanted to give you an idea that one has to really design the cell properly in order to ensure that this cell is going to work. So we just had an idea that one must properly design the cell in order to get proper operation of the I squared L cell. So we shall go ahead with our discussion and the next topic which we shall look at is the different characteristics of the I squared L cell as such that is the noise margin and propagation delays by which you characterize a particular logic family.

Now firstly if you take up the noise margin that is quite obvious, also that the noise margin in a I squared L cell is not going to be too good because of the fact that the voltage levels are constrained to then 0.2 to 0.7 volts at each node because 0.2 volts when the transistor goes to saturation at a node and this voltage cannot exceed 1.7 or slightly more maybe because of the fact that this is a the base voltage of this transistor and it cannot exceed certain value.

So the voltage swings as going to be much low but in the I squared L case, you see that circuit is very peculiar in the sense that there are no resistances in the circuit and so there are no voltage drops across the resistance. It is just the current which is flowing and which is switched either into the base or into the collector of the previous transistor.

So usually the noise margins here are defined in a different way that is instead of defining them in terms of the voltages, here it is defined in terms of current.

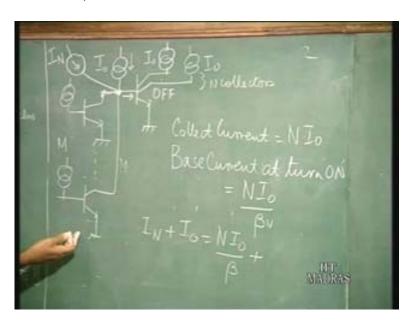

That is how much current noise it can with stand and it is very difficult to get exact figures but some simplistic analysis has been done and the whole idea is how to increase the noise margin. So let us take a very simplistic case again, although we know it is not correct that we assume current sources say this is an n collectors and each of them current sources and let us assume that these current sources have the same value. Although we just done in an analysis, we know that these values are not going to be the same but just to have some idea.

Suppose this transistor is off which means that suppose in this base node you have transistors connected here which again have current sources at their base and there maybe m such transistors. So there are n collectors and here let there be M transistors. This is the M transistors at the base. Now when any of these transistors go to saturation, this current source is going to go this way. The current flows into the collector and this transistor turns off. Now suppose you have another current source here which is due to noise, I will call this IN say noise current and this current flows in here. What is going to happen is if this current is small, again most of the current will be flowing into the collectors of the previous transistors but if this current becomes sufficiently large at this node then this base may get sufficient current to turn it on, from the off state.

So what is this value of this current which turns this transistor on? That is defined as the noise margin in this case. So this is the current source and this transistor is off. So what is this value of noise current which turns this transistor on that is defined as the noise margin in this case. So this is very large that means it can sustain a very large noise current and still remain off. So

how do you calculate this value? So if you have N collectors like this, so the total collector current is N I<sub>0</sub>. So we shall consider that this transistor to turn on, we have to assume certain base current when we say that this transistor is reasonably turned on. So base current at turn on, says N I<sub>0</sub> by beta. Of course this is beta<sub>N</sub> of the NPN transistor. Now at this node if you now write the nodal equation, so what you have is currents flowing in, what you have is IN plus I<sub>0</sub> the currents flowing in equals N I<sub>0</sub> by beta plus here you can have the condition where we can have one transistor on, we can have two transistors on or you can have all M transistor on.

(Refer Slide Time 43:29 min)

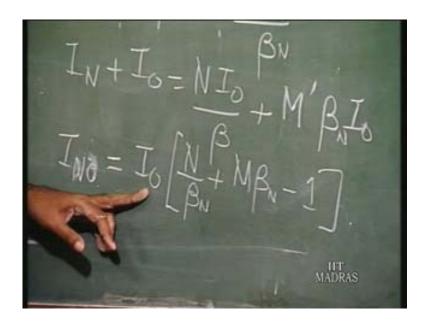

So let us say that M is the number of transistors which is on, I mean M prime or something. So now what is going to happen is if M transistors are on, so this can draw a current of beta times Io, at the base you have a current of Io so these can draw a current of beta times Io. So M prime betan Io. Actually this is called IN O, that is zero because this transistor is in off condition which is equal to Io N by beta plus M betan minus one.

(Refer Slide Time 44:56 min)

The interesting point here is that we have done this analysis with the lot of assumptions involved and we have taken equal currents but the important point which comes out from here that this is proportional to I<sub>0</sub>. The noise current is proportional to I<sub>0</sub>. That is if you want to increase the noise margin, we have to increase I<sub>0</sub>. So the circuit becomes more immune to noise if you increase I<sub>0</sub>. To improve the noise margin one has to have higher injector current, so that is the message from this expression.

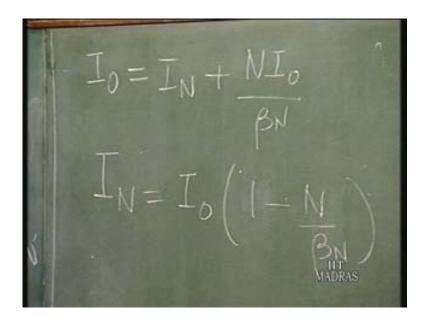

Similarly one can do an analysis when this transistor is on. When this transistor is on this current is flowing into the base, when you turn it on it is simpler because it means that all these transistors connected at the base should be off. So again if you do the case for the transistor being on, what do you have to do is the noise current source, it has to be the other direction. It is basically drawing the current and so this has to be turned off. So what is the condition? Here the condition is the base current, again we will assume that this transistor goes out of saturation when you have this condition, when the base current falls to N Io by betan. So again if you write the nodal equation at that point, so all these transistors are off so they don't contribute to any current. So the current flowing in Io is equal to In plus N Io by betan. So we will have In equals to Io (1-N by betan). So again it is proportional to Io and the noise margin is going to be larger when of course betan is large compared to N and of course this also implies that betan must be greater than N in order to this for this to be positive quantity which is also a condition which we got from the previous analysis which we did, the condition for proper operation of the I squared L cell betan must be greater than N.

(Refer Slide Time 48:14 min)

So again the noise margin is proportional to I<sub>0</sub> so to improve noise margin you must increase the injector current for the I squared L cell. That is the current which is flowing in, if we go back to the figure of the I squared L cell, the current which is flowing in here has to be made; if you want to increase noise margin you have to make it as large as possible but of course that is going to add to the power dissipation.

So again there is a trade of between noise margin and power dissipation. So if we increase the current here flowing into the cell that is if you reduce R because this voltage is around 0.7 to 0.8 volts. So if you reduce R you have larger current which would mean that there is going to be a proportional increase of current flowing through the individual injectors. So that is going to improve the noise margin. So we stop here today, the next class we shall take up the propagation delay problem with I squared L cell that is in fact one of the major problems which I squared L ran into after having such an impressive start, we should say because people thought initially that it is very good circuit but it ran into problem because of propagation delay. We will discuss that in the next class.