## Digital Electronic Circuits Prof. Goutam Saha Department of E & Ec Engineering Indian Institute of Technology, Kharagpur

## Lecture – 51 Digital to Analog Conversion - I

Hello everybody, we are in week 11 of this particular course. In this we will look at Digital to Analog Conversion and Analog to Digital Conversion. So, in today's class we shall take up digital analog digital to analog conversion.

(Refer Slide Time: 00:31)

And before that we shall have a quick recap of what we discussed in the previous week, then need of conversion between analog and digital and 2 techniques for digital to analog conversion; so, that we shall see.

## (Refer Slide Time: 00:47)

Very quickly what we saw in week 10 is how we use Mealy model and Moore model to design synchronous sequential logic circuit. And we had a comparison of these two different modeling techniques. So, in Moore model we had seen that input effects the internal state and output is generated from those states only. So, input does not directly go to the output logic generation.

So, in Mealy model the internal states as well as input together act and to and generate the output of the particular circuit. So, for which we have got certain advantages and disadvantages of both. So, in Mealy model, we can get the output a bit quicker, more number of do not care states, do not care states in the corner map based minimization. And it will be less hardware and in Moore model any tangents in the input circuit is not input signal, is not passed to the output directly.

So, once the tangent stabilized then the clocking happens and then the output is generated from the internal states. So, these are certain things that we had seen and we knew how to convert one model to another. So, we saw the techniques. So, accordingly we can employee them and depending on our requirement, we can use one or the other ok.

So, you also saw algorithmic state machine chart based design techniques, which is a flow diagram based method, it is preferred for larger state machines, because state transition diagram is found in adequate or very complex to read when the number of these variable number of states number of inputs increase ok. And also we saw that state reduction techniques, the usefulness of it and how it can be used to minimize a given synchronous logic circuit and by which we can get a mode you know a simpler circuit ok. So, this is in brief what we discussed in the last week.

(Refer Slide Time: 03:20)

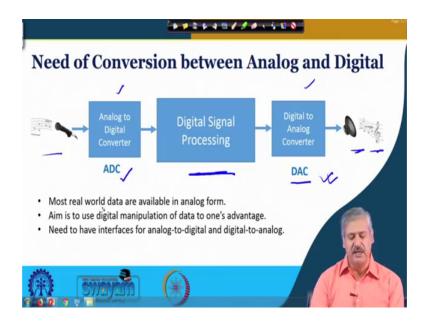

Now, we go to a very important thing about this digital manipulation of signal. So, the most of the real life signal, that we encounter are in are analog in nature. Analog means continuously varying with time and we had already seen that these digital manipulation is of advantages and more about it you will study in some future courses or parallel you are studying in signals and systems or digital signal processing right.

So, what is important is that, we should be in a position to convert analog data to digital ok, analog signal to digital signal. So, for which we need to have a something called Analog to Digital Converter. In brief it is called the abbreviation it is called ADC right. So, consider a sound signal audio signal right.

So, you have captured it through microphone and then analog to digital converter is converting it to a digital stream right. And then you are doing some manipulation over here. So, some frequencies are boosted, some frequencies are you know at innovated and all you are, it is good that you know to have a digital processing technique because of its advantages right. And after that you want to play it in a speaker right, where this speaker will continuously you know change its position and generate the sound wave right. So, for that we need to generate a continuous signal continuous time signal right. So, you need a digital to analog converter over there right. So, this is the kind of thing that we expect when we are trying to manipulate an analog signal in a digital platform right. So, at two ends we will be having analog to digital I mean in one end analog to digital converter and another end digital to analog converter ok. So, this is the interface circuit right. So, in this week we shall look into them right.

So, we begin with digital to analog conversion this part later we shall take up ADC, because in ADC within ADC somewhere a concept of DAC is already there right. So, it is better that we start from DAC right.

(Refer Slide Time: 05:55)

Now, let us see how we can get a digital to analog conversion done. So, remember for a digital to analog conversion the input is digital right and corresponding analog signal is to be generated. So, input is digital means what? Input will be in the form of a you know binary digit say if it is a 4 bit then 1 0 1 0 or 0 0 1 1 or so, if it is a 3 digit 0 1 1 1 0 0 some such thing and output should be a voltage which corresponds to that particular this input digital input combination digital signal ok. So, if it is a voltage otherwise it could be a cadent depending on some continuous time manifestation of the input signal any equivalent manifestation ok.

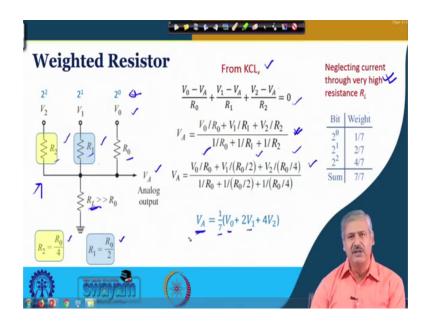

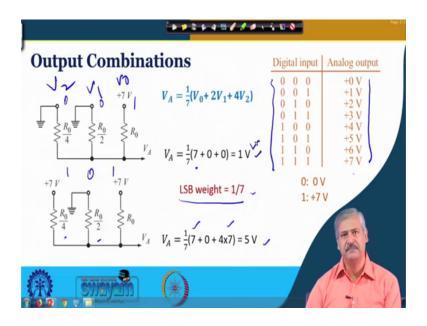

So, let us look into one circuit which is based on weighted resistor right. So, what you see here; what you see here is a circuit where, this is the circuit under consideration. So,

this is your R naught, R 1, R 2 right. And this is your the voltage at this node right and this R L load resistance is very very large, in comparison to the resistances that you have there in this different branches ok.

And to begin with let us not bother about this part ok, 2 to the power 0 etcetera let us just consider these are 3 voltages V naught V 1 V 2 ok. So, this particular circuit just like this how will it operate? So, if we apply KCL at this particular node right since current is very large over here I mean resistance is very large over here. So, the current is very small, so, you can neglect that part right. So, that is what we have mentioned here. So, V naught minus V A by R naught is the current through this V 1 minus V A by R 1 is the current through this and V 2 minus V A by R 2 is the current through this right. So, from KCL it should be equal to 0, is it fine?

Now, if you take all this V A by R naught V A by R 1 V A by R 2 to 1 side and define, then this is the question that you get right. And in this particular equation, if you consider that your R 1 is R naught by 2 ok, R 2 is R naught by 4. So, it is say it is called R weighted resistor ok. So, resistor values are like this right. So, it is R naught divided by some integer power of 2.

So, this is what you get R naught by 2 R naught by 4 and then when you cancel out R naught ok, then what you get here is 1 upon 7 V naught plus 2 V n plus 4 V 2 is it fine. So, this V naught and this is 2 times V 1, this is the 4 times V 2. So, to indicate that we have mentioned this is 2 to the power 0 2 to the power 1 is 2 2 to the power 2 is 4 and you can think of you know extending it beyond that right.

So, the weight final the V A value you get the weight of V naught, in that is what 1 upon 7 whatever the voltage is there it is 1 upon 7 weight of V 1 is 2 upon 7, 2 divided by 7 weight of V 2 is 2 to the power 2 that is 4 by 7 ok. And if you sum it up it will you will get 7. So, this the individual weights, is it clear the basic circuit right.

(Refer Slide Time: 10:00)

Now, if you look at this voltages V naught V 1 V 2, either we put plus 7 volt or 0 volt because these are digital input right either it is high or low. So, you consider high for 7 volt and low for 0 volt right. So, this is one such case 0 0 1 right, then what will happen V naught is 7 volt right, this is your V naught V 1 and V 2 right. And this is 0 0 0 the output will be 1 volt right and if it is 1 0 1 1 0 1. So, this was 0 0 1 this is 1 0 1 right.

So, this is 7 volt, this is 0 volt, this is V 2 0 and this is V 2 V 1 0 V 2 is 7 so, 4 into 7. So, what you get here it is 5 volt right. So, this is the way the output voltage depending on the input combination will be calculated. And if you have all the input combinations digital input combination from 0 0 0 to 1 1 1 ok, you had at the input side, then the corresponding analog output will be 0 volt 1 volt to 7 volt is not it.

And the list these LSB weights the voltage that you can calculate I mean which is also the resolution of it. So, this is 0 volt and this is 1 volt. So, this is 1 volt is what you see as the voltage that it can you know move from one value to another is it clear right. (Refer Slide Time: 11:55)

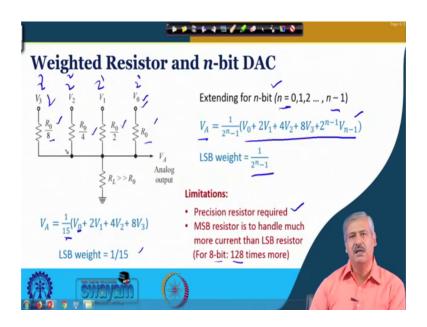

Now, if we extend it to 4 bit, if you extend it to 4 bit what happens? So, this is R naught this is R naught by 2 this is R naught by 4 and you can imagine the next value will be in the weighted resistor based method, it is R naught by 8 right and again if you apply KCL just if you know go on doing that.

Now, it will be the value will be 1 upon 15 plus V naught plus 2 V 1 plus 4 V 2 plus 8 V 3 right. So, this position is to 2 to the power 0 2 to the power 1 2 to the power 2 and 2 to the power 3. These are the corresponding you know binary weights for the digital data that is coming right. And the LSB weight earlier it was 1 upon 7 for the 3 bit case, now 4 bit case it is 1 upon 15 that is whatever the V naught value it will be multiplied by 1 upon 15 right, this is fine.

So, we can extend it to a n bit case and in that case the output voltage over here analog output that you see, for a particular combination of the digital input will be given by this one right. So, this is V naught and this is you know the end part will be your this V n minus 1 for n bit because it starting from 0. So, 0 to n minus 1 right and LSB weight will be 2 to the power n minus 1 is it fine.

So, this is the way we can convert a digital input coming as a big stream to a corresponding analog voltage is it clear right, there will be more associated circuitry and all for practical use. So, that part we shall take up in next class. So, the first part is what we understand how we can convert through a weighted resistor based method.

Now, there are certain limitations that you can visualize for this particular method ok. For which we shall move to another method which is you know found more useful. So, first of all this depends on the weights of the resistors. So, this is we require precision resistor. So, this is one requirement and the second one is the MSB register, this one you can see it is value is R naught by 8 and this is R naught ok.

So, how much current is taken it is? So, this is 7 volt and this is 7 volt. So, this is 1 upon 8 right. So, the current is as much as many times lower I mean higher than this one right. So, for MSB, if it is a 4 bit case, it is 8 times more if it is 8 bit case right. So, it will be 2 to the power 7 because it is a n minus 1 2 to the power n minus 1. So, 128 times more current will be flowing through the MSB ok, MSB resistor right.

So, the loading of it the you know associated issues like heat generation and all is becoming more and more you know troublesome, when the number of beats increase in this particular method ok. This is a simple method, but this is one limitation that we find ok. And today we are talking about larger number of bits used in DAC. So, in that case we need to look at an alternative circuit. So, for smaller number of bits is fine ok.

(Refer Slide Time: 15:31)

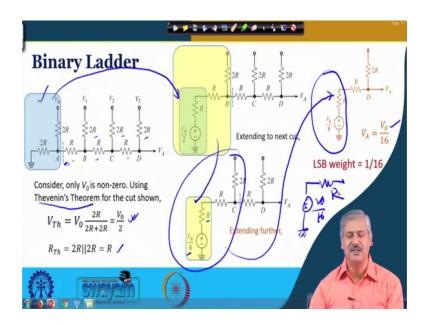

So, for the alternate circuit what we have is called binary ladder ok. This is very very you know useful circuit. So, the binary ladder first we see this structure and then analyse the circuit and then we shall move ahead. So, what you see this also you can see this is a 2 R then R 2 R R 2 R R this is though it has it has been arranged ok. So, there is no such

thing like R naught by 2 R naught by 4 R naught by 8 and so on and so forth I mean becomes some difficult. So, it is all of you know particular type either 2 R or R and it is terminating here with 2 R is it fine.

So, this side further one is V naught then this is V 1 V 2 V 3 earlier we started from this side was V naught you remember that ok. So, this is (Refer Time: 16:23) differences. Now, how we analyse this circuit for which we use what is called Thevenin's Theorem right. So, in Thevenin's theorem, we calculate Thevenin's voltage and Thevenin's resistance right.

So, here for this particular circuit we consider there is a cut over here. And then we see that the circuit is seen from this side to their right hand side from the left hand side to the right hand side. So, this particular block over here we are trying to find the Thevenin equivalent ok. So, for this V naught so, V T h will be V naught into this is 2 R by 2 R plus 2 R right, this is the resistance this is resistance this is open circuit this is cut here right, we know the how the Thevenin theorem work ok.

So, this is V naught by 2 fine and what is the Thevenin equivalent resistance so, 2 R in 2 R in parallel. So, this is R so, this particular block, this particular block can be you know written in this manner with a equivalent circuit obtained from Thevenin equivalent. So, V naught by 2 and this is R is it fine ok. So, this you need to understand from the basics of electrical circuit where Thevenin's Theorem was taught ok.

Now, you look at this larger block this particular block ok. So, you consider all other voltages are not present (Refer Time: 17:57) is there later on we shall include them. So, this V naught by 2 and this is R and R if we consider a cut over here right, then this R and R right 2 R and this 2 R in parallel. So, again in a parallel voltage is the Thevenin voltage Thevenin resistance is R.

And now, V naught by 2 and this is V naught by 2 into 2 R by 2 R plus 2 R. So, it will become V naught by 4 is it fine. So, this is this particular block now comes over here like this right. So, again you consider a cut over here and you will find that this is going over here like this in this particular block right.

And finally, if you further you know move forward. So, you will be having plus minus this is your down ok and this is your R this is your V naught by 16 and this is your is it

fine. So, this is what you are going to get. So, the V over here that is available to the outside world is V naught by 16 and the output resistance is R, is it ok? So, the V naught at the output over here is coming as V naught by 16, is it clear?

(Refer Slide Time: 19:24)

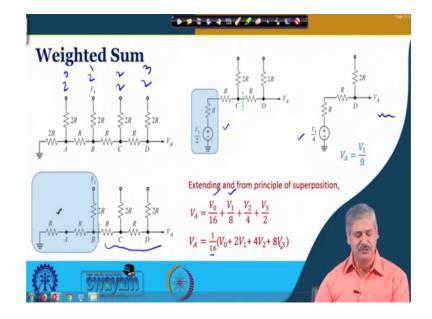

Now, let us look at what happens to the situation when V 1 is present and others are not present ok. So, this is this case ok. So, in this case this 2 R and 2 R are in parallel right and becomes R. So, this is R and R 2 R and this is 2 R and if you take a cut over here, it is similar to what we had seen before only the number of stages to the right hand side is now less one less ok.

So, here first it is becoming V n V 1 by 2 and R then V 1 by 4 R and finally, it will be V 1 by 8 and for this also the output resistance will be R is it ok. So, V 1 contributes as V 1 by 8 in the final thing and this is V naught by 16 and if you extend for all the other voltage input and use principle of superposition you have these output voltage as V naught by 16 V 1 by 8 V 2 by 4 V 3 by 2. And if you add them up then it is 1 upon 16 V naught plus 2 V 1 plus 4 V 2 plus 8 V 3 is not it.

So, will see the 2 to the power 0 comes over here 2 to the power 1 2 to the power 2 and 2 to the power 3 right. So, these are the corresponding binary weights and corresponding analog output will be here this way right, earlier it was 2 to the power n minus 1, now it is 2 to the power n. So, this is for n is equal to 4 that is what we see over here.

(Refer Slide Time: 20:59)

| Bit<br>position<br>MSB<br>2d MSB<br>3d MSB<br>4th MSB | Binary<br>weight<br>1/2 -<br>1/4 -<br>1/8 -<br>1/16 -<br>1/2 <sup>N</sup> , | Output<br>voltage<br>$V/2 \checkmark$<br>$V/4 \checkmark$<br>V/8<br>V/16<br>$\vdots$<br>$V/2^N$ | and DAC<br>Consider, 5-bit ladder<br>0: 0 V<br>1: 10 V<br>LSB: $\frac{10}{2^5} = 0.3125 V$<br>Full scale voltage:<br>10(1 + 2 + 4 + 8 + 16)<br>$2^5$<br>= 9.6875 V<br>$32^3 + \dots + V_{n-1}2^{n-1}$ | <ul> <li>Output impedance always <i>R</i>, regardless of the number of bits.</li> <li>Terminating ladder with 2<i>R</i> impedance, looking into any branch from any node, impedance is 2<i>R</i>.</li> <li>Each digital source sees input impedance as 3<i>R</i>. (equal loading)</li> <li>With 2<i>R</i> termination, full scale o/p voltage = 9.6875 (2<i>R</i>/(<i>R</i>·2<i>R</i>))<br/>= 6.4583 V ~ Current drawn from each digital source for <i>R</i> = 1KΩ is 10V/3KΩ = 3.33 mA</li> </ul> |

|-------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (A)                                                   | SW                                                                          | yam)                                                                                            | ()                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Now, we can extend it for n bit right. So, if we extend it for n bit then, we have for these binary weights corresponding to MSB will be a 1 by 2, second MSB third MSB 1 by 8 and nth MS MSB or the LSB will be 1 upon 2 to the power n right. And corresponding output voltages are V by 2 V by 4 etcetera etcetera and if you have add them up you get the analog output, is it ok.

And if we consider a 5 bit ladder just for an example and you consider 0 as 0 volt the digital binary input that is there and 1 is 10 logic low is 0 volt logic high is 5 you know 10 volt corresponding the binary covalent 0 and 1 ok, then the LSB will be 10 by 2 to the power 5. So, 0.3125 volt right and the full scale voltage right, when all the bits are 1. So, this is 1 plus 10 into 1 plus 2 plus 4 plus 8 plus 16 right your putting those values divided by 2 to the power 5.

So, it is 9.6875 volt it is not 10 volt it is 9.6875 volt ok. So, few interesting thing about this ladder based DAC right. So, in this case output impedance is always R regardless of the number of bits ok. And if you here we have seen that the termination was with that part we have not discussed.

So, if it is terminated with 2 R ok, then looking into any branch; looking into any branch means in the ladder from any node right, the impedance is seen has 2 R. So, that is what you can analyse and see and each digital source. So, this is R and the 2 R. So, it will see a impedance as 3 R so, for the digital source. So, R and 2 R together it is 3 R right.

So, each one of them will be having equal loading right. And if it is not want almost equal loading I mean not much of the difference not like what we had seen in the case of weighted based weighted resistor based method, where it is the MSB was for a 8 bit case 120 times 8 more current you know the resistance was carrying 128 times more current ok.

So, these are certain advantages and instead of 9.6875 ok, if you terminate with 2 R instead of this very high resistance, if you terminate with 2 R then the output voltage will be 9.6875 2 R plus R by R plus 2 R. So, this is 6.4583 volt ok. So, this you will note for the sake off you know your understanding if instead of a very high resistance ok. A some other value is used for termination, then what how you what will be the corresponding voltage, is it fine.

And then the corresponding current will be in that case you know 3.3 3 milli ampere for each one of them for another value. So, it will be you know close to that value it is not varying too much from one digital input source to another this is a good point about this method ok.

(Refer Slide Time: 24:40)

## (Refer Slide Time: 24:42)

So, with this we come to the conclusion of the first part of the DAC discussion. So, what you have seen is that for digital manipulation of analog signal, analog to digital conversion is needed and to get back the processed digital signal digitally processed signal, which is after processing is in digital form and you have to get back it into analog from then digital to analog conversion is needed ok. And we had seen 2 methods in weighted resistor based method in with digital to analog converter DAC has LSB weight of 1 upon 2 to the power n minus 1 and for analyzing that such circuit Kirchhoff's current law KCL is useful ok.

And for DAC used DAC using precision registers ok, the you know for this weighted registered based DAC the precision registers are required and MSB register handles 2 to the power n minus 1 times more current than LSB register this we have already seen. And binary ladder based das DAC has got width for the LSB as 1 upon 2 to the power n and Thevenin Theorem is useful to analyse such circuit and it has a constant output impedance with respective of number of bits, then it can have equal loading for each input is digital input which is a useful feature. So, with this we conclude this particular lecture.

Thank you.