# Digital Circuits Prof. Santanu Chattopadhyay Department of Electronics and Electrical Communication Engineering Indian Institute of Technology, Kharagpur

# Lecture – 21 Arithmetic Circuits (Contd.)

So, this look ahead carry generation part this portion; so, we can make it a design which is again an iterative design.

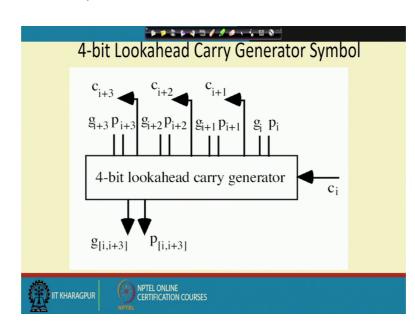

(Refer Slide Time: 00:18)

Suppose I have got this 4-bit look ahead carry generator circuitry; so, that has got c i as input and it generates of course, this a i and b i those x i and y I those bits are there. So, it is not shown here explicitly. So, this g i and p i; so, they are coming here in terms of that x i and y i. So, that part is not shown here and it generates this c i plus 1 c i plus 2 c i plus 3 and it generates this a p i plus i 2 i plus 3 and g i 2 i plus 3; so, those portions.

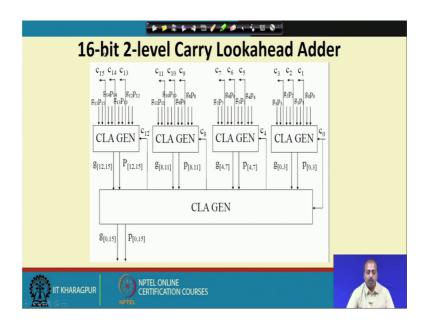

## (Refer Slide Time: 01:00)

Now, if you have got that this carry look ahead generator 4-bit versions. So, now, you can use it for 16 bit carry look ahead circuitry; so, we have got this 4 such carry look ahead blocks connected. And these carry look ahead blocks; so, they are getting say this say this say g 0, p 0, g 1, p 1, g 2, p 2 etcetera and it is generating 2 generate one generate signal and one propagate signal. So, this generate signal will be will be fed to this CLA generator circuit.

So, this is actually this block is similar to this block; so, whatever be the number of the inputs here similar number of inputs are there in this CLA generator block also and we are just using some sort of hierarchical structure ok. So, this is using the same CLA generator block, but it is this of this g inputs are coming from this the corresponding CLA generator block of the previous level of hierarchy.

And it is generating g 0 to 15 and p 0 to 15 that is the if you take a 16 bit block then this will be the generate signal from the 15 bit block and this will be the propagate signal from the 16 bit block and this is the propagate signal from the 16 bit block.

## (Refer Slide Time: 02:27)

|                                                            | **********                                                                                                   |               |

|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|---------------|

| Operation of                                               | of 16-bit 2-level Carry Looka                                                                                | ahead Adder   |

| Signals<br>computed                                        | Formulas                                                                                                     | Delay         |

| <b>g<sub>i</sub>, p</b> i<br>i=015                         | $\mathbf{g}_{i} = \mathbf{x}_{i}\mathbf{y}_{i}$<br>$\mathbf{p}_{i} = \mathbf{x}_{i} \oplus \mathbf{y}_{i}$   | 1 gate delay  |

| g <sub>[ii+3]</sub> , p <sub>[ii+3]</sub><br>i=0, 4, 8, 12 |                                                                                                              | 2 gate delays |

| $g_{[i.i+3]} = g_{i+3} + p_{[i.i+3]} = p_i p_{i+1}$        | $\begin{array}{l}g_{i+2}p_{i+3}+g_{i+1}p_{i+2}p_{i+3}+g_{i}p_{i+1}p_{i+2}p_{i+3}\\p_{i+2}p_{i+3}\end{array}$ | 3             |

|                                                            | EL ONLINE<br>TIFICATION COURSES                                                                              |               |

So, you can cascade another such block here ah; so, to get a 32 bit block ok; so, that way we can go ahead. So, we can we will looking to an example; so, these are simple formulas that are we have got this delay calculations and all like this g i p i. So, the formula is g i equal to x i y i; so, that is that will 1 1 gate delay and this p i computation is x i x or y i; so, that is also 1 gate delay.

Now, this g i 2 i plus 3 and p i 2 i plus 3 they follow this particular formula and here if I am if I am assuming to 2 level realization of the circuit; then that there is one set of and gates that will be realizing this g i plus into p i plus 3 similarly g i plus 1 into and p i plus 2 and p i plus 3. So, this way it will be realizing the AND terms and after that there will be an OR term. So, there will be 2 gate delay in the generate g i 2 i plus 3 and p i 2 i plus 3.

# (Refer Slide Time: 03:21)

|   |                                              | 2643180                                                                                 |               |     |

|---|----------------------------------------------|-----------------------------------------------------------------------------------------|---------------|-----|

| - | 16-bit 2-lev                                 | el Carry Look                                                                           | ahead Add     | ler |

|   | Signals<br>computed                          | Formulas                                                                                | Delay         |     |

|   | $c_4, c_8, c_{12}$<br>$g_{[015]}, p_{[015]}$ |                                                                                         | 2 gate delays |     |

|   |                                              | $c_8 = g_{[47]} + g_{[03]}$<br>$p_{[811]} + g_{[03]} p_{[47]} p_{[811]} + c_{[03]}$     |               |     |

|   |                                              | $\substack{\text{811} \\ p_{[1215]} + g_{[47]} p_{[811]} p_{[1}}{p_{[811]} p_{[1215]}}$ | 215]          |     |

|   | $p_{[015]} = p_{[03]} p_{[47]} p_{[47]}$     | 0[811] P[1215]                                                                          |               | A   |

|   |                                              | NLINE<br>ATION COURSES                                                                  |               |     |

So, for this c 4, c 8 and c 12; so we will have 2 gate delays for g 0 to g 0 15 and p 0 15 that will also have 2 gate delays.

(Refer Slide Time: 03:33)

| 16-bit 2-                                                                          | level Carry Lookah                                                                      | ead Adder     |

|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|---------------|

| Signals<br>computed                                                                | Formulas                                                                                | Delay         |

| C <sub>i+1</sub> , C <sub>i+2</sub> , C <sub>i+3</sub><br>i = 4, 8, 12             |                                                                                         | 2 gate delays |

| <i>i.e.,</i> c <sub>5</sub> , c <sub>6</sub> , c <sub>7</sub> , c <sub>9</sub> , ( | c <sub>10</sub> , c <sub>11</sub> , c <sub>13</sub> , c <sub>14</sub> , c <sub>15</sub> |               |

| $c_{i+3} = g_{i+2} + g_{i+3}$                                                      | $_{1}p_{i+2} + g_{i}p_{i+1}p_{i+2} + c_{i}p_{i}p_{i+1}p_{i+2}$                          |               |

| $c_{i+2} = g_{i+1} + g_i g_i$<br>$c_{i+1} = g_i + c_i p_i$                         | $p_{i+1} + c_i p_i p_{i+1}$                                                             |               |

|                                                                                    | TEL ONLINE<br>RTIFICATION COURSES                                                       |               |

Now for this c i plus 1 i plus 2 i plus 3 for I equal to 4 8 and 12; they will see 2 gate delays; so, because of this expression if you looking into this expression; so you will see how many gate delays are necessary.

# (Refer Slide Time: 03:47)

|                                                                                   | *******                                              | 8            |   |

|-----------------------------------------------------------------------------------|------------------------------------------------------|--------------|---|

| 16-bit 2-lev                                                                      | vel Carry Looka                                      | head Adder   | • |

| Signals<br>computed                                                               | Formulas                                             | Delay        |   |

| $s_{i+1}, s_{i+2}, s_{i+3}$                                                       |                                                      | 1 gate delay |   |

| i = 4, 8,                                                                         | 12                                                   |              |   |

| <i>i.e.</i> , s <sub>5</sub> , s <sub>6</sub> , s <sub>7</sub> , s <sub>9</sub> , | $s_{10}, s_{11}, s_{13}, s_{14}, s_{15}$             |              |   |

| $s_i = p_i \oplus$                                                                | c <sub>i</sub>                                       |              |   |

|                                                                                   | Þ                                                    |              |   |

| Total:                                                                            | 8 gate levels in the CL<br>32 gate levels in the rij |              |   |

|                                                                                   | nline<br>Attion Courses                              |              |   |

So, this way it can total 8 gate levels in thus carry look ahead adders versus 32 gate levels in the ripple carry adders. So, if I am if I am had having a 16 bit adder then there will be 32 gate level in the ripple carry adder because this individual stage it will have that sum and carry. So, that will be the carry come calculation will have 2 stages ok. So, that way it will have total 32 stage, but this if you are using this carry look ahead mechanism; so, that will have only 8 stage.

That is why this carry look ahead adder; so they are going to be much faster than this ripple carry adder and in many application; so where we need fast addition, subtraction. So, we go for this carry look ahead adder instead our ripple carry.

Of course the penalty that we pay is the number of gates that are needed becomes very high. So, this is the thing that I was talking about.

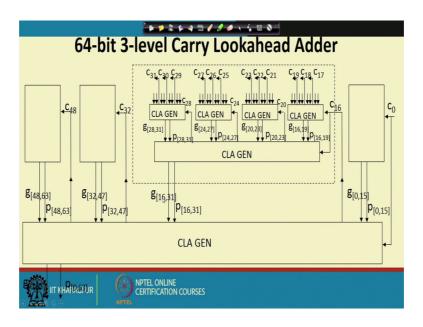

(Refer Slide Time: 04:45)

So, this is suppose I have called this 16 bit carry look ahead blocks ok. Now from there; so, I can I can have some 32 bit block and from there I can have some 64 bit block. So, here it is 64 bit block that is generated that is shown here in terms of this cascading of this clock generator circuit.

(Refer Slide Time: 05:00)

|  | 64    | <mark>4-bit 3-level Carry Lookahe</mark>                                                                                                                         | ad Adder      |  |  |  |  |

|--|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--|--|--|--|

|  | Level | Signals computed                                                                                                                                                 | Delay         |  |  |  |  |

|  | PRE   | g <sub>i</sub> , p <sub>i</sub> i=063                                                                                                                            | 1 gate delay  |  |  |  |  |

|  | 1     | $g_{[ii+3]}, p_{[ii+3]}$ i=0, 4, 8, 12,, 56, 60                                                                                                                  | 2 gate delays |  |  |  |  |

|  | 2     | g <sub>[ii+15]</sub> , p <sub>[ii+15]</sub> i=0, 16, 32, 48                                                                                                      | 2 gate delays |  |  |  |  |

|  | 3     | $g_{[063]}, p_{[063]} \qquad c_{16}, c_{32}, c_{48},$                                                                                                            | 2 gate delays |  |  |  |  |

|  | 2     | $c_{20}, c_{24}, c_{28}, c_{36}, c_{40}, c_{44}, c_{52}, c_{56}, c_{60}$                                                                                         | 2 gate delays |  |  |  |  |

|  | 1     | $c_{21}, c_{22}, c_{23}, c_{25}, c_{26}, c_{27},, c_{61}, c_{62}, c_{63}$                                                                                        | 2 gate delays |  |  |  |  |

|  | POST  | s <sub>21</sub> , s <sub>22</sub> , s <sub>23</sub> , s <sub>25</sub> , s <sub>26</sub> , s <sub>27</sub> ,, s <sub>61</sub> , s <sub>62</sub> , s <sub>63</sub> | 1 gate delay  |  |  |  |  |

|  |       |                                                                                                                                                                  |               |  |  |  |  |

And these are different gate delays calculation that we have; so it is similar to the previous calculation.

# (Refer Slide Time: 05:06)

| Delay           | of a l |                                    | -Lookahead                      | d Adder |

|-----------------|--------|------------------------------------|---------------------------------|---------|

| T <sub>lo</sub> | okahea | $_{d-adder} = 4 \left[ c \right]$  | og <sub>4</sub> k               |         |

|                 | k      | T <sub>lookahead-adder</sub>       | T <sub>ripple-carry-adder</sub> |         |

|                 | 4      | 4                                  | 8                               |         |

|                 | 16     | 8                                  | 32                              |         |

|                 | 32     | 12                                 | 64                              |         |

|                 | 64     | 12                                 | 128                             |         |

|                 | 128    | 16                                 | 256                             |         |

|                 | 256    | 16                                 | 512                             |         |

| IT KHARAGPUR    |        | PTEL ONLINE<br>RTIFICATION COURSES |                                 |         |

So, in that in summary you can say that a a look ahead adder; so, now total it has a carry bit k bit carry look ahead then the total look ahead adder delay is 4 into log of k. So, that gives the advantage like k equal to say if I have got the adder size has a 32, then look ahead adder delay will be 12 stages and this ripple carry adder will have 64 stages. So, that ways for 256 bit add addition; so, look ahead adder will have got a delay of 16 stages and carry look ahead ripple carry will have 512 stages; so that is pretty high.

(Refer Slide Time: 05:46)

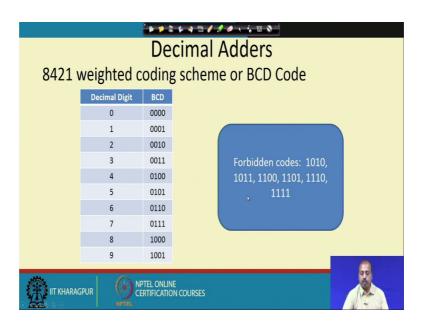

Next will be looking into decimal adders; so, decimal adder means that I have got the binary coded decimal digits BCD and then I want to add them. So, in case here; so here I have got the digits important for 0 to 9 only; so rest are not important. So, they are coded like this; so, 9 is coded as 1001 and rest of that 4-bit combinations are not valid for the BCD addition; so, these are the forbidden codes 1010, 1011 and all.

(Refer Slide Time: 06:19)

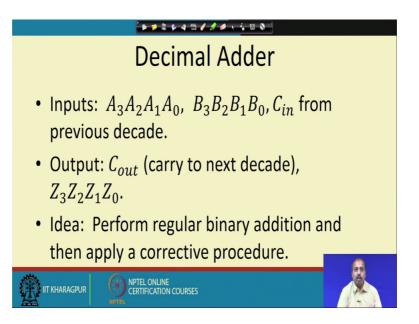

So, for decimal adder; so, we have got the inputs A 3, A 2, A 1, A 0, B 3, B 2, B 1, B 0 and C in from the previous cascade state. And output was C out and Z 3, Z 2, Z 1, Z 0 and so what we do for decimal adder is that we perform regular binary addition and then we do some corrective procedure.

## (Refer Slide Time: 06:40)

|    | Comparing Binary and BCD Sums |   |                       |                       |                       |                |                            |                 | ims            |                       |                |          |

|----|-------------------------------|---|-----------------------|-----------------------|-----------------------|----------------|----------------------------|-----------------|----------------|-----------------------|----------------|----------|

|    | Decimal Sum                   | K | <b>P</b> <sub>3</sub> | <b>P</b> <sub>2</sub> | <i>P</i> <sub>1</sub> | P <sub>0</sub> | -Շ <mark>Sam</mark><br>out | eZ <sub>3</sub> | Z <sub>2</sub> | <i>Z</i> <sub>1</sub> | Z <sub>0</sub> | Cout is  |

|    | 0-9                           |   |                       |                       |                       |                | -                          |                 |                |                       |                | set to 0 |

|    | 10                            | 0 | 1                     | 0                     | 1                     | 0              | 1                          | 0               | 0              | 0                     | 0              |          |

|    | 11                            | 0 | 1                     | 0                     | 1                     | 1              | 1                          | 0               | 0              | 0                     | 1              |          |

|    | 12                            | 0 | 1                     | 1                     | 0                     | 0              | 1                          | 0               | 0              | 1                     | 0              |          |

|    | 13                            | 0 | 1                     | 1                     | 0                     | 1              | 1                          | 0               | 0              | 1                     | 1              |          |

|    | 14                            | 0 | 1                     | 1                     | 1                     | 0              | 1                          | 0               | 1              | 0                     | 0              |          |

|    | 15                            | 0 | 1                     | 1                     | 1                     | 1              | 1                          | 0               | 1              | 0                     | 1              |          |

| 12 | 16                            | 1 | 0                     | 0                     | 0                     | 0              | 1                          | 0               | 1              | 1                     | 0              | 22       |

|    | 17                            | 1 | 0                     | 0                     | 0                     | 1              | 1                          | 0               | 1              | 1                     | 1              |          |

So, for example here we have got this number 0 to 9 for this part it is same ok. So, actually this likely shifted; so, this is for 0 to 9 if the decimal sum is equal to 0 to 9 then it is same; however, if the decimal sum is 10; 1010. So, it will be represented in the BCD forms; so they will be they will be represented has carry bit being 1 and the Z 3, Z 2, Z 1, Z 0 being 0.

Similarly, for 11 if the decimal sum is 11 then the C out will be equal to 1 and the Z 0 will be equal to one and the rest of them will remain as 0 12 will be like that. So, basically this C out bit will be set to 1 whenever the sum becomes greater than 9 for the BCD addition ok. So, this way I can ah; so, C out is 0 for this part and for other part; so, it will be equal to 1.

(Refer Slide Time: 07:36)

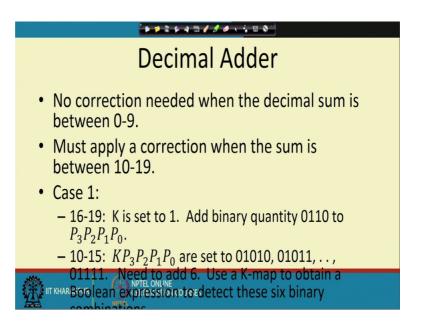

So, no correction is needed when the decimal sum is between 0 and 9 and we must apply a correction, when the sum is between 0 and 19. So, at most we can add 2 9 and 9; so that is at most the value can be 18. So, this one a value the between 0 and 10 and 19; so, you have to do some correction.

(Refer Slide Time: 08:00)

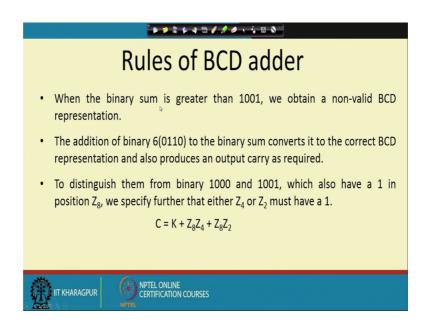

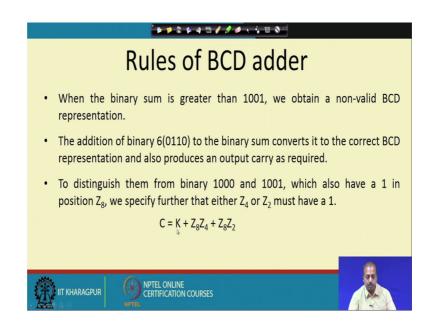

So, this; so, these are the rules for BCD addition. So, when the binary sum is greater than  $1 \ 0 \ 0 \ 1$  we obtain a non valid BCD representation. And the binary the addition of binary 6 to the binary sum; it will convert the number to the correct BCD form.

So, whenever it becomes more than 1001; so, you just add this 6 to the binary to the to whatever sum you have got and that gives the corrective action. So, to distinguish between 1000; that is binary 1001 and 1001; so, which will also have one in position Z 8. So, we specify that either Z 4 and Z 2 must have a value 1. So, C is equal to K plus Z 8, Z 4 plus Z 8 Z 2.

(Refer Slide Time: 08:46)

So, this is the BCD sum part; so, this is 0100; so, this will be added if this Z 8, so, that if Z 8 K 4.

(Refer Slide Time: 09:00)

So, if you look into this expression is K plus Z 8 Z 4 plus Z 8 Z 2. So, if this is situation then only the carry is generated.

(Refer Slide Time: 09:07)

So, what we are doing? For with this 4-bit addition result; so, you are trying to add this 6, but that is conditional conditional subject to the case that there was a carry or this Z 8, Z 4 was equal to 1 or Z 8 Z 2 was equal to 1.

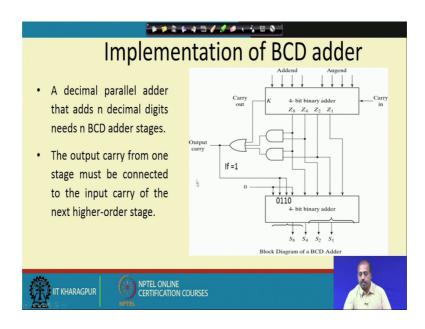

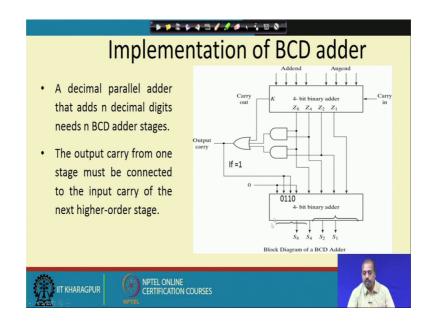

So, if you draw the corresponding truth table then will find that under these conditions; so, we need to do the correction of adding 6 to the binary addition result to get the BCD addition. So, a decimal parallel adder that adds n decimal digits needs a n bit; n BCD adder stages. And the output carry from one stage must be connected to the input carry of the next higher stage; so, that is obvious.

So, if you need more number of decimal digits to be added. So, then this entire block has to be repeated one after the other to get the BCD addition for higher number of digits.

(Refer Slide Time: 10:00)

(Refer Slide Time: 10:08)

|                                                                                                 | · · · · · ·                                            |

|-------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| Two bit Multi                                                                                   | plication                                              |

| a     b     a b       0     0     0       0     1     0       1     0     0       1     1     1 | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

| IT KHARAGPUR NPTEL ONLINE<br>NPTEL CERTIFICATION COURSES                                        |                                                        |

Next we look into the multiplier; now you see that if I have got 2 bits a and b has input then the multiplication is like this a b a and b it is 0 1 0 0 1. So, if you compare with the AND operation you see that you are getting the same thing. So, this AND is some sort of 2 bit binary multiplication; so, this 2 bit binary multiplication is same has the AND of the 2 bits.

# (Refer Slide Time: 10:34)

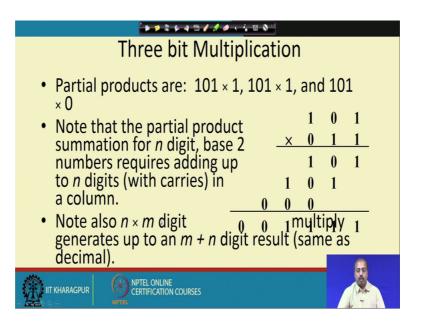

For 3 bit multiplication; so suppose; so we have will generate this partial product terms, so  $1 \ 0 \ 1 \ 1 \ 0 \ 1$ ; so, this  $1 \ 0 \ 1$  multiplied by 1. So, that generates this partial term  $1 \ 0 \ 1$  then this  $1 \ 0 \ 1$  multiplied by the second one that generates this partial sum and then multiplied by 0 that generates this partial sum and then we have then we add all this partial sum to get the result.

So, we have the partial products and this partial product summation for n digit base 2 numbers requires adding up the up to n digits in a column. So, that way we are going to add these digits. So, that if I am multiplying and n by one n bit number by an m bit number, then we have to generate it will generate and m plus n digit number ok.

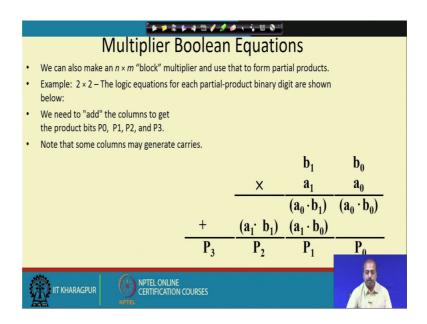

## (Refer Slide Time: 11:25)

So, that is they of they are from multiplication. So, Boolean equation for multiplication; so, it will be like this. So, if I am taking as a 2 bit multiplication for example, then this generates a 0 b 0 and a 0, b 1 as the this partial sum. And then this a 1, b 0 and a 1, B 1 as another partial sum then this partial sums are added the P 0, P 1, P 2, P 3 that generates the product terms ok.

(Refer Slide Time: 11:52)

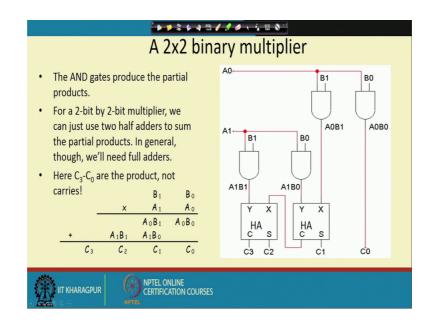

So, this is the circuitry for that; so, this generates A 0, B 0; then this generates A 0, B 1 A 1, B 0 and A 1, B 1 and then this A 0, B 0 directly gives; it is not added with anything.

So, that that come directly comes at the multiplication the result output C 0; then this A 0, B 1 and A 1 B0 are to be added.

So, I can use a half adder here because there is no carry. So, I can just use a half adder to do that and then from this some carry may be generated and that carry has to be added with A 1, B 1. So, this A 1, B 1 and that carry comes and that will generate the sum C 2 and the carry C 3.

So, this way I can use this circuitry to get a 2 by 2 binary multiplier.

(Refer Slide Time: 12:43)

|   | ★★★★★★★★★★★★★★★★★★★★★★★★★★★★★★★★★★★★                                                                             |

|---|------------------------------------------------------------------------------------------------------------------|

|   | Multiplication: a special case                                                                                   |

| • | In decimal, an easy way to multiply by 10 is to shift all the digits to the left, and tack a 0 to the right end. |

|   | 128 x 10 = 1280                                                                                                  |

| • | We can do the same thing in binary. Shifting left is equivalent to multiplying by 2:                             |

|   | 11 x 10 = 110 (in decimal, 3 x 2 = 6)                                                                            |

| • | Shifting left twice is equivalent to multiplying by 4:                                                           |

|   | 11 x 100 = 1100 (in decimal, 3 x 4 = 12)                                                                         |

| • | As an aside, shifting to the <i>right</i> is equivalent to <i>dividing</i> by 2.                                 |

|   | 110 ÷ 10 = 11 (in decimal, 6 ÷ 2 = 3)                                                                            |

| - |                                                                                                                  |

Now, some special cases; so, in decimal an easy way to multiply by 10 is to shift all digits to the left and put a 0 to the right end. So, 1 to 8 multiplied by 10; so, we know the result is 1 2 8 and a 0. So, you shift the numbers digits by to the left and put a 0 at the right end. So, for the same thing we can do with binary one.

So, so we can shift left is equivalent to multiplying by 2. So, a shifting left is multiplying by 2; so, for example, this 1 1 multiplied by 1 0 is in decimal system it is 3 into 2 which is is equal to 6. So, if you converted into binary notation; so, it is 1 1 0.

So, what has happened is that this 1 1; so, it has been left shifted and this less significant bit position we have put a 0 ok. So, that gives the binary shifting or this multiplication by 2 and if you shift it twice; shift left twice then it is a multiplication by 4. So, for example,

this 1 1; so, if I left shift twice then I will get 1100 and this number is nothing, but 12. So, this 3 into 4 is 12; so, this is basically left shifting by 2 bits.

So, shifting to the right is equivalent to dividing by 2. So, if you are ah; so for example, this 110 that is 6. So, if you are shifting it by right position; so, you are shifting it right means this 0 will go. So, 1 1 will remain; so, that is 1 1 the result is 3 this is nothing, but 6 divided by 2 is 3.

So, this multiplication and multiplication by 2; so, this is basically left shifting the number by one position, multiplication by 2 power i is left shifting the number by i positions and similarly division by 2 is right shifting the number by one position and division by 2 to the power i is right shifting the number by i positions.

So, this way we can have the special cases for multiplication by multiplication and division by powers of 2.

(Refer Slide Time: 14:50)

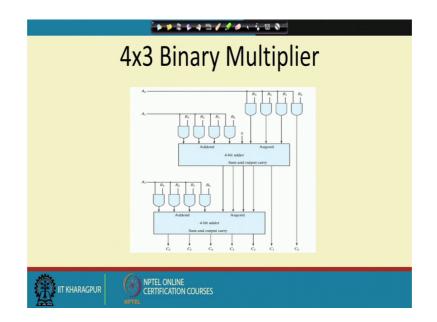

So, for 4-bit multiplication; so 4 by 3 binary multiplier; so, we have got one 4-bit input B 0, B 1, B 2, B 3 and we have got 3 bit input A 0, A 1, A 2. So, what we can do? So, we can generate these partial sums in this fashion ok. So, then they can be passed through some adders ok; so, two 4-bit adders will be necessary and we can passed them through the adder and ultimately we can get this sum which is consisting of 7 bits. So, 8 C 0 to C

6 plus there will be an another carry; so, 4 plus 3; 7, the result may be 8 bit also. So, that way there will be another carry generated ok.

So, this way we can have this partial sums generated and we can do the multiplication. Of course, this multiplication process that we have talked about is pretty slow and in case of integrated circuit chips particularly in VLSI domain. So, even find many other efficient multiplication algorithm that have come up. So, this is the basic multiplication algorithm that we have discussed and the idea is to see how can we do it using logic gates and all.

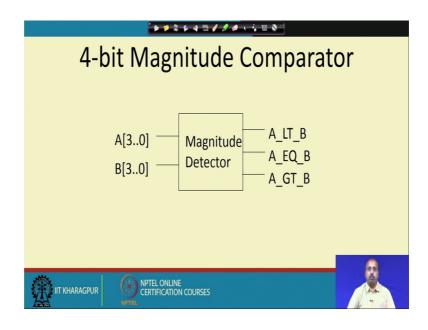

Next we will be looking into another very important arithmetic module which is known as magnitude comparator. So, I have got 2 inputs I need to tell whether the one of them is equal to the other greater than the other or less than the other.

(Refer Slide Time: 16:21)

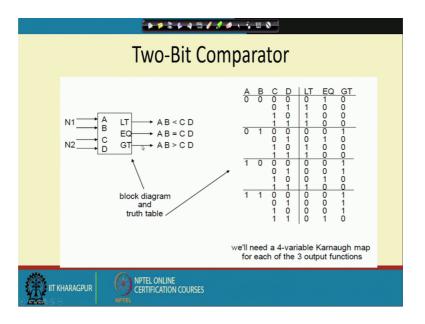

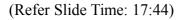

So, if I have got a two-bit value; so, it is like this. So, see suppose AB is the first number and CD is the second number. So, what is what is happening is that this AB is AB is 0 0; then if CD is 0 then it less than is 0, equal is 1 and greater than is 0 that is these 2 numbers are equal. So, this EQ output is 1 and this less than and greater than these 2 out puts are 0.

Similarly, if AB is 0 0 and CD is 0 1; so, this less than output is 1 equal output is 0 and this greater than output is 0. Then this is 1 0 again the same thing; so, this is this AB is 0

0. So, whatever be the CD apart from 0 0 this less than will be 1, others will be 0. So, this way I can draw a truth table for I can make a truth table for writing the entire behavior of this block of the this comparator block.

So, for doing the minimization; so, we will need 4 variable Karnaugh map for each of this 3 output functions ok. So, it 4 variable Karnaugh map and accordingly you can do the minimization, get the circuitry and ultimately we can say it is less than equal to and greater than these 3 outputs we can see we can I will draw the corresponding logic circuit.

So, this is the thing; so K map for less than is A bar, B bar, D plus A bar, C plus B bar CD EQ is this one ok. So, this A bar, B bar, C bar, D bar or A bar, B C bar C bar D that is either A and B actually the logic is that A and B both are 0 C and B should also be 0. A is 0, B is 1; so C should be 0 and D should be 1. So, this way I can do it.

So, this equality; so if you if you look it look into it more carefully; so, we can find that the this can also be written has A x nor C and B x nor D ok; that way it can be there.

(Refer Slide Time: 18:22)

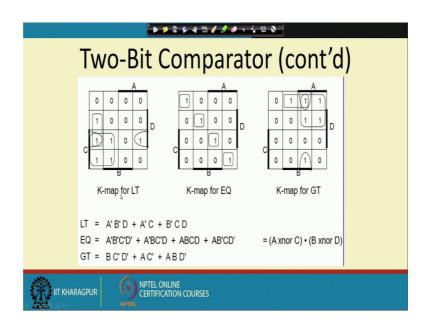

So, this is the; so,. So, that way we can draw the corresponding truth table and from there I can get the logic functions realized in terms of basic logic gates. Now let us look into to this equality comparator more carefully; suppose I have got only 2 bits to be compared and I have say whether the bits are equal or not. So, in terms of truth table; so, if it is 0 0 then the output is 1, if it is 0 1; it is 0 1 0 is 0 and 1 1 is also 1, for these 2 cases it is 1.

Now, you see the this truth table correspond to simple XNOR logic. So, it is a 2 input XNOR gate; so, this is what is happening here. So, Z is equal to X XNOR Y; so, this XNOR gate is an equality comparator.

(Refer Slide Time: 19:20)

| 4-bit Equality Detector                             |  |

|-----------------------------------------------------|--|

| A[30] Equality<br>B[30] Detector A_EQ_B             |  |

| IIT KHARAGPUR NPTEL ONLINE<br>CERTIFICATION COURSES |  |

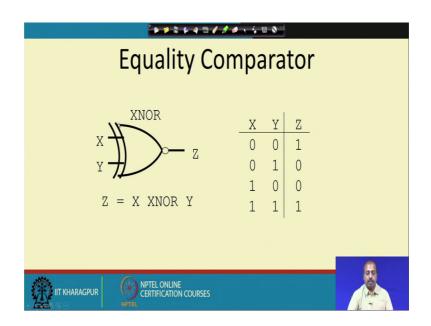

So, if I have if I need a 4-bit equality comparator equality detector; then this may be the blog diagram of that. So, I have got this A 4-bit input A 3, A 2, A 1, A 0 and similarly B 3, B 2, B 1, B 0. So, this is the this is the B 4-bit B input and it answers A equal to B. So, this output is 1 only when this A and B input this A and B input are equal to each other.

(Refer Slide Time: 19:37)

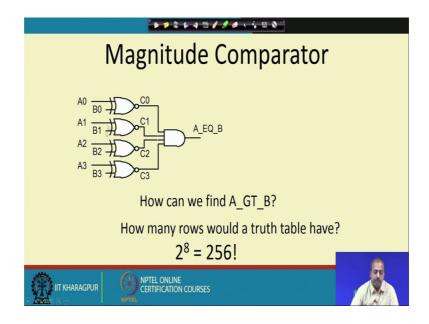

So, I can take a very simple circuit consisting of 4 XNOR gates this A 0 A 0 and B 0 fed to the first XNOR A 1, B 1 fed to the next X NOR like that. And now this C 0, C 1, C 2,

C 3; so, they are; they are to be anded. So, this AND gate is not; so, they are to be anded to get A equal to B ok; so, that can be a 4-bit equality comparator.

(Refer Slide Time: 20:00)

But what about magnitude comparison like; so not only equality, I also want less than and greater than output. So, the A is less than B or A is greater than B.

(Refer Slide Time: 20:15)

So, equality is definitely fine; so how can we get A greater than B. So, how many rows in the truth table have? So, if you try to answer this question then since there are 8 inputs A

0 to; since we have got 8 inputs A 0 to A 3 and B0 to B 3; total number 8 input say if I am trying to draw a truth table; so, there will be 256 entries.

So, if I am trying to draw a Karnaugh map; then it is an 8 variable Karnaugh map that we have to minimize. So, that is a very clumsy way that is way very; so for in our course we have seen that we can draw K map up to 6 variables not more than that. So, that makes it difficult; so we have to do some something else for getting the minimized form.

$\begin{array}{c} & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\$

(Refer Slide Time: 21:00)

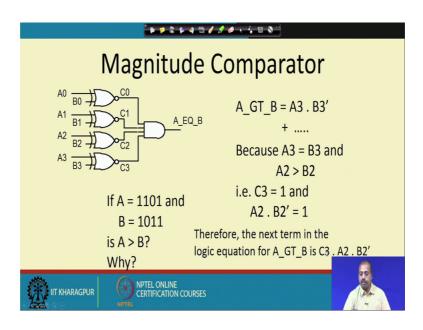

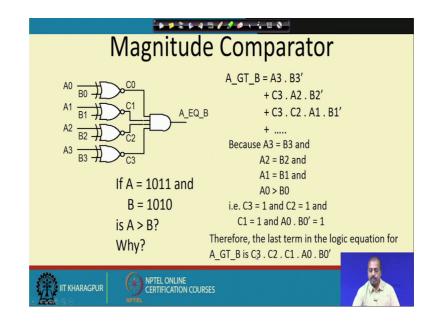

.So, if you see that if A equal to 1001 and B equal to 0111 then A is greater than B; why? This is because this most significant bit A 3 is equal to 1 here and B 3 B 3 is 0 here; so A is greater than B. Now because A 3 greater than B; so A 3; so the condition is A 3, B 3 dash or A 3, B 3 bar is equal to 1.

(Refer Slide Time: 21:36)

Now, one term in the logic equation for A greater than B is A 3, B 3 bar. Now what about this one? Say if I have got A equal to 1101 and B as 1011. So, here also A is greater than B because the first 2 bits A 3 and B 3 were same and A 2 was 1 and B 2 was 0. So, I can say that A 3 is equal to B 3 and A 2 greater than B 2 that is why I have got C 3 equal to 1. So, C 3 equal to one if A 2 B 2 dash equal to 1 and A 3 equal to B 3.

So, we have got ah; so, so C 3 was A 3 equal to B 3 ok. So, the C 3 was a 3 equal to B 3; so, the conditions becomes C 3 and A 2 and B 2 bar B 2 B 2 dash.

(Refer Slide Time: 22:22)

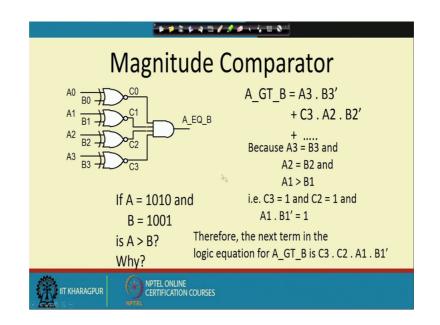

That way if we just shift by one more position; so, you will get the condition one more condition there. So, that will be this is the thing A 3 equal to B 3, A 2 equal to B 2 and A 1 greater than B 1. So, we have got C 3 equal to 1, C 2 equal to 1 and A 1 B 1 dash equal to 1.

So, we see that the A 3 greater than A greater than B terms becomes C 3 and C 2 and A 1 and B 1 bar.

(Refer Slide Time: 22:51)

And naturally, I will have one more stage where it will be doing this B 0 also like only the B; B 0 A 0 and B 0 bits are differing. So, if ah; so, this is the situation the A 0, B 0 dash is equal to 1, C 3 equal to 1, C 2 equal to 1 and C 1 equal to 1. So, I will get the last term as C 3, C 2, C 1; A 0, B 0 dash.

(Refer Slide Time: 23:15)

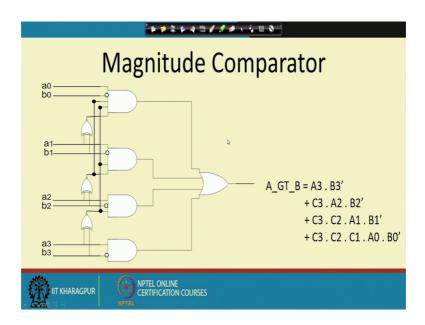

So, the final expression becomes like this; so, A greater than B is A 3 B 3 dash plus C 3 A 2 B 2 dash plus C 3 C 2 A 1, B 1 dash plus C 3, C 2, C 1; A 0, B 0 dash. And this can be realized by this circuit you see that we have got a very clean circuit here and we do not take help of the Karnaugh map and all. So, sometimes that makes that process makes it very difficult and we have to use some other logic to come to the circuit.

(Refer Slide Time: 23:54)

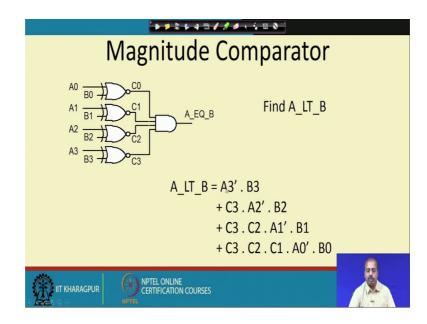

So, similarly you can say A less than B A less than B is given by this formula A 3 dash B 3. So, A 3 is 0 and B 3 is 1 or A 3 B 3 are same detected by this condition C 3 and A 2 bar

A 2 is 0 and B 2 is 1 or C 3, C 2 that is A 3, B 3 are same A 2, B 2 are same and A 1 is 0 and B 1 is 1 and this condition A 3, B 3 same A 2, B 2 same A 1 B 1 same and A 0 is 0 and B 0 is 1. So, that way I can write down the condition for A less than B.

(Refer Slide Time: 24:24)

Next, we will be looking into another important topic which is known as code converters. So, many a times we want to convert one numbers coded in some number system into some other number system. So, that is that is known as code converters; so, they coded in different form.

(Refer Slide Time: 24:45)

# A code converter is a logic circuit that changes data presented in one type of binary code to another type of binary code, such as BCD to binary, BCD to 7–segment, binary to BCD, BCD to XS3, binary to Gray code, and Gray code to binary. We know that, two digit decimal values ranging from 00 to 99 can be represented in BCD by two 4–bit code groups.

So, this is our code converter it is a logic circuit that changes data represented in one type of binary code to another type of binary code. For example, BCD code to binary code, binary code to BCD code BCD to 7 segment binary BCD to 7 segment display code, then binary to BCD; BCD to XS 3 code, so like that binary to gray code gray to binary code.

So, there are different types of codes that are there and many a times we need to interchange between this type this type of code. So, ok; so, how to do this code conversion? That we will see now; so, 2 digit, 2 digit decimal values ranging from 0 0 to 99 can be represented by BCD BCD by 2 4-bit code groups; so, that can be utilized for doing this conversion.

(Refer Slide Time: 25:36)

| BCD-to-Binary Conversion                                         |

|------------------------------------------------------------------|

| One method of BCD-to-Binary code conversion uses adder           |

| circuits :                                                       |

| 1. The value, or weight, of each bit in the BCD number is        |

| represented by a binary number                                   |

| 2. All of the binary representations of the weights of bits that |

| are 1s in the BCD number are added                               |

| 3. The result of this addition is the binary equivalent of the   |

| BCD number                                                       |

| A                                                                |

| TIT KHARAGPUR ON TELL ONLINE CERTIFICATION COURSES               |

|                                                                  |

So; first will be looking into BCD to binary conversion, so one method for BCD to binary conversion is by some adder circuit. So, value or weight of each bit in the BCD number is represented by a binary number and all of the binary representations of the weights of bits that are 1 in the BCD number; they will get added. So, this way we can have some adder circuitry and using that adder we can convert the BCD number to binary number.

(Refer Slide Time: 26:08)

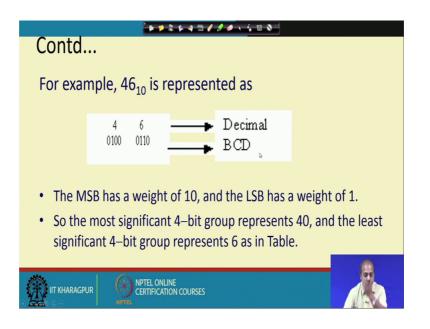

So, it is like this. So, 46; so 46 this is the 4 is this is the notation and 6 this is the thing. So, this is the decimal number and this is the BCD number. Now this most significant bit it has got a weight of 10 and the least significant bit has a weight of 1.

So, the most significant 4-bit group represents 40 and the least significant 4-bit represent group is 6 ok. So, because this is this weight is 10 and this weight is 1. So, this is 4 into 10 plus 6; so that we can do.

(Refer Slide Time: 26:44)

| · · · · · · · · · · · · · · · · · · · |                        |                            |                        |                        |                    |                |                |                    |  |

|---------------------------------------|------------------------|----------------------------|------------------------|------------------------|--------------------|----------------|----------------|--------------------|--|

|                                       |                        | Bit position               |                        |                        |                    |                |                |                    |  |

| Decimal<br>weight                     |                        |                            |                        |                        |                    |                |                |                    |  |

| Binary<br>weight                      | 2 <sup>3</sup>         | 2 <sup>2</sup>             | 2 <sup>1</sup>         | 2 <sup>0</sup>         | 2 <sup>3</sup>     | 2 <sup>2</sup> | 2 <sup>1</sup> | 2 <sup>0</sup>     |  |

| B CD bit                              | 2 <sup>3</sup> x<br>10 | 2 <sup>2</sup> x<br>10     | 2 <sup>1</sup> x<br>10 | 2 <sup>0</sup> x<br>10 | 2 <sup>3</sup> x 1 | $2^2 \ge 1$    | $2^1 \ge 1$    | 2 <sup>0</sup> x 1 |  |

| Weight                                | 80                     | 40                         | 20                     | 10                     | 8                  | 4              | 2              | 1                  |  |

| Bit<br>designation                    | h                      | g                          | f                      | е                      | đ                  | с              | b              | a                  |  |

| 4610                                  | 0                      | 1                          | 0                      | 0                      | 0                  | 1              | 1              | 0                  |  |

|                                       |                        | 40                         |                        |                        |                    | 4              | 2              |                    |  |

|                                       | 6.                     |                            | Maiah                  | + Tobl                 |                    | _              | -              |                    |  |

|                                       |                        | IPTEL ONLIN<br>ERTIFICATIO | N COURSES              | t labi                 | <u>e</u>           |                |                | A                  |  |

So, we can say that this bit position; so, this is decimal weight is bit position 1 and bit position 0. So 10 to the power 0 and 10 to the power 1 so, if the binary weight of that. So, if you look into that number at weight 10 and look into the corresponding. If you look into the corresponding binary number binary weights, this is 2 power 0 1 2 and 3. So, the BCD number; the BCD bit weight is 2 power 3 into 10, this is 2 power 2 into 10, this is 2 power 1 into 10 and 2 power 0 into 10.

Now, so for example, this 46; so 46 it has got 0100. So, this 0 gives a contribution of 0 then this; so, this 4 this 4 is represented by the first 4 bits and the 6 is represented by the next 4 bits. And for the first 4 bits they have got a weight of 10 now this numbers; so, now this 0 multiplied by 10 that gives me 0; 1 1 is. So, this is 2 power 2; so, that is 4 multiplied by 10 that gives me 40, then this is 2 multiplied by 0 2 power 1 into that value is 0; so that is that is giving me 0.

So, that way; so this part gives me 10 and this part gives me 6.

(Refer Slide Time: 28:11)

| The binary equivalent of each BCD bit is a binary number |                  |                |                       |  |  |

|----------------------------------------------------------|------------------|----------------|-----------------------|--|--|

| representing the BCD bit weight                          |                  |                |                       |  |  |

|                                                          | BCD bit position | BCD bit weight | Binary representation |  |  |

|                                                          | а                | 1              | 1                     |  |  |

|                                                          | 6                | 2              | 10                    |  |  |

|                                                          | С                | 4              | 100                   |  |  |

|                                                          | d                | 8              | 1000                  |  |  |

|                                                          | е                | 10             | 1010                  |  |  |

|                                                          | f                | 20             | 10100                 |  |  |

|                                                          | g                | 40             | 101000                |  |  |

|                                                          | h                | 80             | 1010000               |  |  |

|                                                          |                  |                |                       |  |  |

|                                                          |                  |                |                       |  |  |

So, so binary equivalent of each BCD bit will be is a binary number and it is represented as a BCD weight bit. So, this is BCD position a, b, c, d, e, f, g, h as we have seen here this bit designation a, b, c, d, e, f, g, h. So, they have got this BCD weight values like this and corresponding binary representations like this ok. (Refer Slide Time: 28:39)

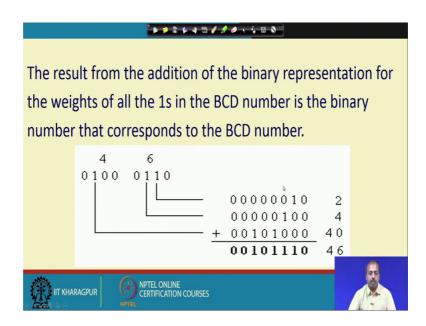

So, this way we can do this binary to BCD conversion like the result from this addition of binary representation of the weights of all the ones in the BCD number. So, that will give me the corresponding binary numbers.

So, this is ah; so 0 4 is 0 1 0 0; so that is represented if you take the corresponding weight and all; so, value was 40; so that is giving you. Similarly this was these 2 these bit is 1 and this bit is 1 and for the these bit; I know that the corresponding weight is 4 ok. So, this 4 is added and for these bit I know the corresponding weight is 2; so, this 2 is added. So, these gives me this number; so after doing this all this additions. So, it gives me 46 in the binary number.

(Refer Slide Time: 29:20)

| **********                |                                                       |  |  |  |  |

|---------------------------|-------------------------------------------------------|--|--|--|--|

| Example:<br>Convert the E | CD equivalent of 26 to binary.                        |  |  |  |  |

| Solution                  | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ |  |  |  |  |

|                           | NPTEL ONLINE<br>CERTIFICATION COURSES                 |  |  |  |  |

So, similarly suppose I have to convert this 26 into binary. So, again we do we do the same thing that; so, this part is all of them they will contribute to 10 and this this is 2 power 0 1, this is 2 power 1 2, 2 power 2 4 and this is 8.

So, this is this is 2; so, 2 into 10; so that gives me 20. So, I write down the binary representation for 20 then in thus in this part. So, this part is this weight is 10 power 0 for this all the 4 bits the weight is 10 power 0. So, this is this bit is 1, 2; so 2 into 10 power 0 that is 1; so that that gives me 2; so, I write down the binary representation for 2. Similarly, here I write down the binary representation for 4 and I sum them up; so, this gives me the binary 26.

So, in this way we can convert BCD numbers to equivalent binary numbers; of course, we have got other avenues. So, we can have a truth table and write down the corresponding Boolean functions for doing this conversion also; as well.