## Course name- Analog VLSI Design (108104193) Professor – Dr. Imon Mondal Department – Electrical Engineering Institute – Indian Institute of Technology Kanpur Week- 5 Lecture- 21, module-02

Welcome back. So, up until now in the last few lectures, we have been concentrating on various topologies of a single transistor circuit with the aim of designing various control sources and we saw that our our humble common source amplifier was a voltage control current source right. So, voltage control current source an example of voltage control current source was a common source amplifier right. So, let me write it write it out fully right. Then we saw a voltage-controlled voltage source with a gain of 1 right approximate gain of 1 which was common drain amplifier. Then we saw current controlled current source which had common gate amplifier right.

What was the what were the characteristics? Characteristics where the primary characteristics were in terms of the Rin and Rout Rin and Rout for a voltage control current source Rin should be high Rout should be low right. How high with respect to what? High with respect to Rin should be high with respect to the source resistance and Rout should be low with respect to the load resistance right. So, if I have to sketch if I have to write it appropriately I should say Rin should be much much greater than Rs and Rout should be much much less than or ratheRin this case is a current source right, Rout should be much much greater than RL and a common source amplifier was satisfying that. What about a voltage control voltage source? In case of a voltage control voltage source, what was the requirement? The requirement was Rin should be much greater than Rs and however, in case since it is a voltage source which means its output resistance should be ideally 0, but 0 is not possible.

| VICS - Common Source Amp. | Pin<br>Rs         | Pout-<br>>> R_ |

|---------------------------|-------------------|----------------|

| VCVS n Drain "            | >> kg             | << R_          |

| cccs _s " gate "          | $\ll R_{\rm s}$   | >> R           |

| CC VS - 22                | << P <sub>3</sub> | << P_          |

So, it should be much much lesser than RL. In case of a current control current source I was we wanted the current input to go in without getting divided which means input resistance should have been much much lesser than Rs and it is a current source at the

output side. So, output resistance should be much much greater than RL right. So, what other voltage sources what other control sources remain? Clearly you see that one is absent from this and that is a current controlled voltage source. What is the Rin and Rout requirement for that? It is a current control source which means Rin should be much lesser than Rs right ideally should be 0.

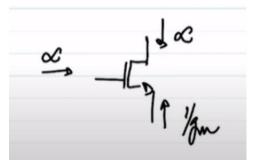

What is Rout? Rout should be much lesser than RL or ideally should be should be 0, but what is the topology? As it turns out if you just simply take a transistor if you just simply take a transistor and let us quickly run through why we could do the other three topologies by simply connecting the sources and the loads at certain terminals. We were able to do because the transistor has two high impedance nodes and one low impedance node right. So, a transistor biased in saturation has drain impedance to be infinity right at least that is what our model is predicting gate impedance is obviously infinity. However, the source impedance looking in is 1 over gm right. So, this the source is the low impedance and other two are the high impedance.

Now, when we wanted to when we wanted Vccs or Vcvs we could as well connect in case of Vccs we could we wanted two nodes of a transistor which were high impedances and that is available. In case of a Vcvs we wanted one node high impedance, input node high impedance, output node to be low impedance that was also possible because input node was the gate output node was the source. In case of current control voltage source we wanted the input node to be low impedance output node to be high impedance that is also possible because in input node was source and output node was drain. But now we want now you now you want a now you now you want two nodes which are of low impedance right that is the requirement of a current control voltage source and clearly we do a transistor in itself does not provide you two low impedance nodes. So, which means we have to we have to change course and we will have to think about this problem in a slightly different way.

So, that is what we will do in the rest of this lecture. So, let us see. So, before we proceed into getting into getting into how to design a current control voltage source let me take a slight amount of detool and talk about negative feedback. So, what is negative feedback? What do we understand by negative feedback? So, in a very layman term a negative feedback is a phenomena by which we observe certain output and take a corrective action

based on what the output actually is and how what the output actually should be right. Take for example, you are riding a bicycle when you are riding a bicycle you know that you have a path that you are that you are traveling right.

So, let us say you need to take a turn let us say you take need to take a turn in the road and the control knob is your handle right. So, when you are taking a turn you know the direction in which you want to go, but when you are driving the bicycle the bicycle might or might not go in the direction that you want. So, in your mind what are you doing? You are trying to figure out if there is a difference between the direction in which you want to go and the direction in which you are actually going. If there is a difference then you are taking corrective action by turning the handle right. You are taking a corrective action to turning by turning the handle and in your mind you are trying to figure out whether the difference between the actual wherever you want to go sorry wherever you want to go and the where you are going the difference between those two are getting minimized or not right.

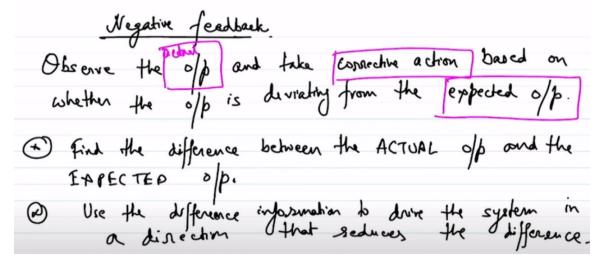

So, in a very layman terms negative feedback means observing observe the output whatever the output might be and take corrective action based on whether the output is exp is deviating from the expected output right. So, there are three things here one you need to observe the actual output observe the actual output right you need to observe the actual output also you need an expected output because you need to know where you are going if you do not know where you are going then there is no point in taking any action. So, you need to know where you are going you need to observe where you are actually going and then based on that difference you need to take a corrective action correct. So, if we have to tabulate these if we have to tabulate this action or if you have to itemize this action what we need to what we are essentially saying we are saying that find the difference between the actual output and the expected output right. So, that is that is number 1, number 2 is use the difference information to drive the system in a direction that minimizes the difference or reduces the difference right instead of minimizes let me say reduces right.

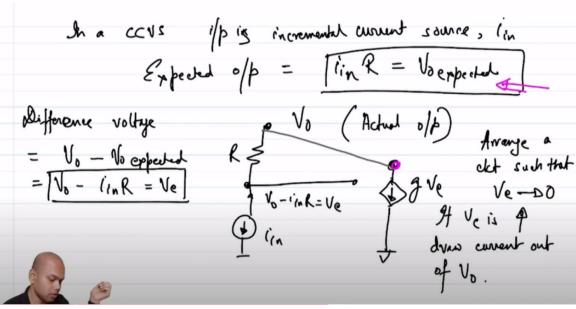

So, that is in essence how a any negative feedback system works now depending on whether it is a electrical system or mechanical system or electromechanical system or even a biological system you will have to you will have to put the system together in order to achieve this action right. So, let me show you with an example hopefully I will be able to convince you. So, let us say we want to design a current control voltage source right. So, in a current control voltage source what is the expected output firstly what is the input? Your input in a current control voltage source my input is Iin a current source right input is a current source Iin let me write input is a current source is a. In this case let me say it is a incremental current source because all these things are in incremental domain see this previous input is incremental current source Iin and output is expected output right this is expected output is input is Iin times output is a voltage right Iin times some constant and that constant let us say is R right.

So, it is a voltage source at the output input is that input is current output is voltage which means there has to be a change of there has to be a change there is a change in unit right. So, the proportionally constant if you have to go from current to voltage is a resistance. So, let us say this is value a resistance of value Iin times R right. So, we need to we need to figure this out right expected output is this is supposed to be Vout Vo expected ok. So, how should we arrange this? So, let us say we want to we have a voltage source rather Let us say we have a output Vo we want to ensure that is Vo effectively becomes equal to Iin times R and you have an R you have an Iin right let us say you have an Iin you have a current source Iin ok.

So, this is the expected output what is the real output real output it is obviously the output node that you are that you are observing right. So, this is the Vout is the actual output. So, you have to find you have to find a difference between the real output and the expected output. So, how do you find a difference Rin other words yeah. So, how do you find a difference we need to find a difference.

So, difference voltage is what? Difference voltage is equal to Vo minus Vo expected right which is Vo minus Iin times R. Let me call this Verror because this Verror it it it by I mean instead of writing difference voltage all the time we let us call it something I call it error Verror why am I calling it Verror I am calling it Verror because ultimately what is the goal the goal is to make Vo is equal to Iin times R if we are achieve if we achieve the goal successfully then what will be this error voltage the error voltage will go to 0 and if it does not go to 0 what what what is it implying it is essentially implying that we have not been able to successfully make a current control voltage source which is supposed to give a output of Iin times R that is all it is saying right hence the nomenclature error. So, ideally we should we should arrange our circuit in such a way that the error voltage goes to 0 fine. So, first which means that we need to we need to so let me also write it down arrange a

circuit such that Ve tends to 0 ok. So, then I mean if we have to arrange something to make Ve tends to 0 then obviously we will have to ensure that we will have to ensure that we first generate Ve.

So, how do you generate Ve if you have Vo you have Iin you want Ve Ve is Vo minus Iin times R it is pretty simple what you do you you you drag out a current of Iin from Vo through a current through a resistance R right. So, if I simply do this what will be this voltage this voltage will be Vo minus Iin times R which is Ve ok. So, what do we need to do again let me remind you of the other fact that a current control voltage source or rather when we have this Iin right when we have this Iin this Iin might have an Rs if we have a proper current control voltage source this relation should hold even if you have an Rs that is the whole purpose of putting a current control voltage source right. If we just simply pull Iin push Iin into R I will always get an output voltage which is equal to Iin times R, but that is not the goal because if we have if we do that then I am then the output voltage is susceptible to the source resistance Rs and precisely we do not want that that is why the input resistance has to be much less than Rs right. So, anyhow so let us we will come back to this discussion point in shortly, but for the time being let us try to design a circuit in which we can arrange a circuit in such a weather once we have a Ve we need to drive the output in such a weather Ve tends to 0 ok.

So, what should we do let us think about it. So, let us assume that Ve is not 0 right let us say Ve is positive right if Ve is positive oRLet me say if Ve is increasing right if Ve is increasing what is it telling us if Ve is increasing what is it telling us it is essentially telling us that the current that I am drawing out right the current that I am drawing out from Vo is not sufficient right that is what I am being told if Ve is increasing which means which means the current that I am drawing out of Vo is not sufficient I have to increase the current that I am drawing out of Vo right if lincrease the current that I am drawing out of Vo then I will be it is likely that I will be reducing the voltage at Vo right if I pull current out of a node the node the node voltage reduces ok. So, now, one might say that I already have a current source Iin. So, should Iincrease Iin I cannot do that because Iin is not in our control right Iin is a source that has been given to you by it is a independent source you cannot go and control it. So, what we need here we need a dependent source because we are taking we should be taking a directive action based on the information of Ve not if Ve is increasing then draw current out of Vo right.

Similarly, if Ve is decreasing what should we do we should push current into Vo right. So, let us let us stick to the Ve is increasing case. So, if Ve is increasing we need to draw current out of Vo. So, so what is the action attempts that I am interested in input what to whatever stuff that I put here I have to put something here. So, that if Ve increases I draw current out right if Ve increases I draw current out of Vo correct.

So, essentially we want an incremental voltage control current source right we need a incremental voltage control current source right. So, so let us put that let us put an arbitrary voltage control current source then we will see whether it is realizable or not right. So, let us see let us say we put a voltage control current source right and let us say this voltage control current source has a proportionally constant let us say some g like some g times Ve. So, if Ve is increasing in the that and the way I have drawn I am drawing current out of I am drawing current out of this node what is the requirement if V increasing V increases I should draw current out of Vo what should I do I can simply connect these two these two terminals right let me draw it in a next page in a cleaner manner. So, what I am essentially saying is this.

So, this is Iin. So, this is g times Ve this is Ve and I need to connect Vo to the top terminal

of the voltage control current source right ok. So, so this seems to be this seems to be the logic right. So, let us run through the logic once again what is this telling you this is telling us that if Ve increases I am pulling current out of Vo and if Ve decreases I am pushing current into Vo right this is all incremental. So, I should actually use a small notation right. So, that was a mistake let me use a small notation here g times Ve ok.

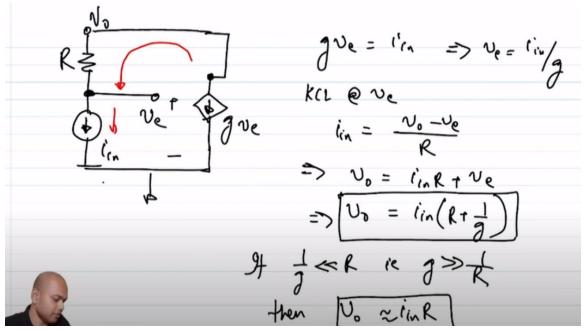

So, let us see let us see if this satisfies our case of firstly what is the thing that we need to see we need to see whether what is the input and output relation that is the first thing what is the second thing you need to see we need to check whether we are able to satisfy the input output resistance criteria as well right. So, what is Vo? So, let us let us write KCL let us write KCL at which note would you like to write KCL at. So, let us let us write KCL at Ve. So, what is Iin what is the direction of Iin Iin is this this is Iin where is Iin flowing out from there is only one loop.

So, Iin is flowing this loop. So, what is g times Ve. So, g times Ve is equal to Iin which means Ve is equal to Iin over g right right. So, KCL at Ve what does it give what do we get we get Iin is equal to Vo minus Ve over R right which means Vo will be equal to Iin times R plus Ve which means this is equal to Iin times R plus 1 over g. So, this becomes Vo what did we want we wanted Vo to be equal to Iin times R, but we have a extra factor. So, but note that this g is in our control because we have put it right it is not it does not come with the with the with the source or the load information right.

So, if g is much much greater than R sorry if 1 over g g if g is much much greater than or ratheRLet me in this write in this way if 1 over g is much much less than R I e g is much much greater than 1 over 1 over R then Vo seems to be equal to Iin times R this is approximately equal to Iin times R then it looks like this can mimic our voltage control current source, but hold on we have not yet established whether the input output resistance criteria are satisfied right. So, let us do that next R this is Iin this is R this is Iin this is g times Ve where this is Ve right. So, this is this is my Vo. So, let us say I put the Iin here. So, that I can understand where the ports are right let us let me use a different color for the input Iin.

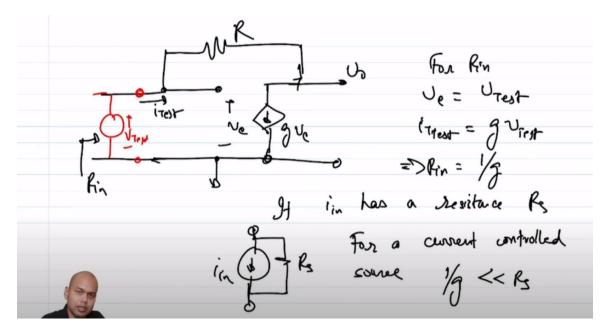

So, this is the port input port and this is the output port this is this is the R correct ok. So, what is the input impedance what we need to do in order to find out input impedance. So, for Rin we have to find impedance firstly we have to desensitize all the sources right. If you have to de energize Iin which means you set Iin to be 0 if Iin to be 0 then the current source goes off current source going off means it is an open circuit.

So, this is what your network is. Now, you have to find out the input and the output impedance what do you think is the input impedance what is Rin how will you find I Rin

for Rin again you do the same old same old we apply a test voltage right you apply a test voltage and then you go around and find out what the test current is what is the what is the test current in this case you have again you have a single loop in this case VE becomes equal to V test right for Rin VE is equal to V test which means this current right which means I test whatever is the I test will be equal to G times V test which means Rin will be equal to 1 over G ok.

So, if the volt if the current source has a resistance Rs right if the current source has a if Iin has a resistance Rs that is if Iin comes with a resistance Rs for a for a current control source we need to ensure 1 by G is much much less than Rs right again note that this is in our control because this contraption is something that we have put in. So, what about the output impedance what will you do to find out the output impedance same old same old. So, again the source does not play a part because Iin goes to 0 this is what we are left with this is Ve G times Ve we apply a test voltage at the output terminal we find out what is I test right. So, clearly that no current flows here because other side is ground open.

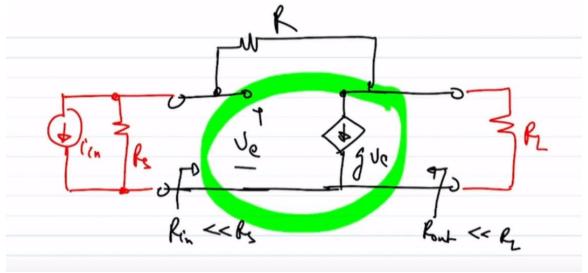

So, this terminal becomes Vtest which means G times Ve becomes I test I mean this is the entire I test. So, which essentially means I test is equal to G G times V test which means Rout also is equal to 1 over G which essentially means that if we have an RL while driving a load RL ensure 1 over G is much much less than RL for voltage source correct. So, what does our final incremental model look like in the presence of sources and loads this is what it looks like. So, let me draw the contraption first. So, this is VE this is G times VE this is R these to go out this is the input Iin with a source resistance RS and this is RL right.

So, this will behave like a voltage control sorry this will behave like a current control voltage source right. If we honor two conditions one is in this particular case in this particular contraption what do we need to honor we need to honor Rin should be much less than RS and Rout should be much less than RL. Now, note that if we do the full blown analysis in the presence of both RS and RL in the presence of both RS and RL the conditions that you will get will not be exactly equal to this right. So, this is these conditions of Rout and Rin that I have derived is under the condition that only either RS or RL is present. So, if you do the calculations in this case in the presence of RS and RL you will get a slightly different result, but nevertheless it is still in your control to ensure that this circuit can behave like a voltage current control voltage source.

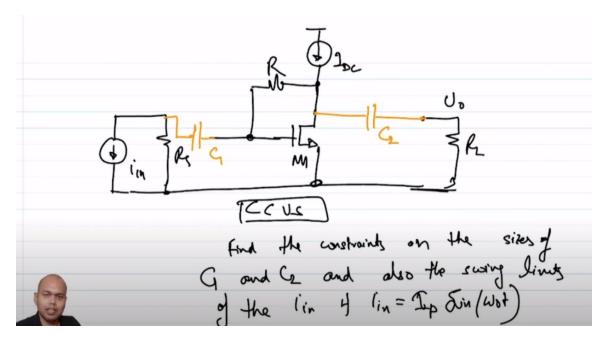

So, now, we I mean now you should readily recognize what is this contraption what is this contraption G times VE this clearly is a MOSFET right what is that G that G m is the transconductance of the MOSFET. So, now, let us replace the incremental model with its with this full blown equivalent. So, this becomes again this is Iin this is RS right and we have RL and instead of G times VE we have to put a MOSFET, but this ground this is source source is grounded right. So, it is rounded we have a resistance between the drain right. So, this let me mark the terminals here this should be the drain this should be the source this should be the gate correct.

So, we have a resistance between drain and the gate correct. So, we have a resistance

between the drain and the gate and then we will have to ensure that the inputs are also connected right. So, how do you want to connect the input I mean we would like to connect the input I mean the same way as we have been doing we would like to connect the input through AC coupling capacitor. So, let us say we put a coupling capacitor here right let us say C1 it is a coupling capacitor here let us say C2 right this is R, but I mean you might be now screaming at me saying that how have I biased the transistor M 1 this is clearly not biased because what is its gate to source voltage what is the current flowing through it clearly nothing right the gate to source voltage is not applied it is 0 in this case right. So, what should I do I can simply put a current source right we can put a current source bias where do we want to put in this case it seems like since I already have a connection between the drain and the gate right the connection between drain and the gate is already established the easiest thing to do will probably be to mimic that condition in which we observe the drain and feedback at the gate right.

So, this can be the IDC bias ok. So, this will be you know Vo ok. So, what I would request you to do this because so this essentially becomes my full blown current control voltage source with biasing in picture what I will request you to do is find the constraints on the sizes of C1 and C2 and also the swing limits of Iin if Iin is equal to Ip sin omega naught ok. So, I mean this will be your assignment for the week this will be one of the assignments for the week it might be instructive to go through it on your own right ok. I will see you in the next class.