Information Theory, Coding and Cryptography Dr. Ranjan Bose Department of Electrical Engineering Indian Institute of Technology, Delhi

> Module - 26 Convolutional Codes Lecture - 26

Hello and welcome to our next module on Convolutional Codes.

(Refer Slide Time: 00:33)

Let us start with a brief outline for today's talk. We would discuss what we mean by tree codes and convolutional codes followed by the notion of trellis codes. This is an interesting class of codes with memory then we will understand how we do encoding using trellis codes. And finally, we look at the polynomial description followed by the generator polynomial matrix specifically for convolutional codes. So, that is the brief outline for today's talk.

(Refer Slide Time: 01:08)

Now, let us see what we have done so far. So far we have looked into different kinds of linear block codes including cyclic codes, BCH codes, Reed Solomon codes, and several other examples, but there were all codes without memory. What we want to do today is look at a different class of codes with memory.

(Refer Slide Time: 01:32)

So, the block codes that we have studied so far always had a one to one correspondence between what is the input information block, or the information word and the output word or the codeword always. So, if you have the same information word coming in you would always look up in the lookup table and give out the same codeword right.

So, this is useful for high data rate applications and the incoming stream of data is broken up into blocks, each block is encoded and we have seen very good codes like reed Solomon codes with beautiful distance properties and very efficient code rates. Now the large block lengths also suffer from a basic disadvantage. Even though they give you very efficient codes we cannot declare the results of decoded output until the entire block is received and decoded.

(Refer Slide Time: 02:20)

So, we cannot start declaring the results, so if the block consists of say 1024 bits and we are working at 10 kilobits per second. Then there is a tangible amount of delay possible before we start declaring results and this may not be very conducive for real time operations. But there is another class of codes that we are going to study today where the delay is minimal and that what we will study is the convolutional codes today which works using information frames of length k naught which are in just a few bits.

So, please note earlier the k the information word used to be 253 bits or a 473 bits, they large or even thousands of bits long. But here the information frames that we will deal with will be just a few bits 1, 2, 3. So, we will be working with much smaller sets of symbols which will be used to encode and each information frame would result in a codeword frame of length n naught.

So, what we are doing different is k naught symbols or bits will be encoded into n naught symbols or bits where both k naught and n naught are small. So, we would have not just the usage of the input frame information frame to generate the codeword frame we would also use memory ok. So, we would use the stored information of previous m information frames, and we would together use the current frame and the previous m frames to declare what is the resultant codeword frame.

So, it should be obvious that the same information frame may not lead to the same codeword frame because we do not know what is sitting in the memory.

(Refer Slide Time: 04:43)

So, let us talk about codes with memory right. We have mentioned that previous m information frames are used to obtain a single codeword frame, so we are going to rely on memory right. So, such codes which are based on this memory and obtained in this fashion are called tree codes, a subclass of tree codes which we will use in real world are the convolutional codes we will formally define that today right.

Now, up to now the decoding techniques that we have discussed for linear block codes are algebraic and memoryless. But here we have to go one step further and figure out how to decode codes with memory because it is not just a lookup table we have to keep track of what was in the memory. So, the state the memory becomes important so, we must have a state space diagram to understand how the encoder is working. So, the convolutional codes make decisions based on the past information and therefore, memory is an integral part.

If you look at a block encoder here you have this information frames coming in of size k and n blocks coming out, but we will have a different structure for codes with memory.

(Refer Slide Time: 06:18)

So, what we assume is that we have an infinitely long stream of in incoming symbols and this is not a bad assumption. Because we have um over deluge of data in today's world and we do not really complain about too many input symbols coming in.

So, first we break up this input bit stream into k naught symbol blocks or frames we will use the word frames to distinguish from the block codes that we have used earlier. Now each segment which is called a frame will be encoded, but the encoder is it consists of two parts a memory which is basically a shift register and a logic circuit associated with it. So, these two are the ingredients that form the encoder for a convolutional code.

The memory which is a shift register is capable of storing m previous information frames. So, each time a new information frame arrives it is shifted into the shift register, but in order to do. So since, the size of the shift register is limited the old the oldest information frame has to be discarded only then it will make room for the new information frame to come in. So, at any time m into k naught symbols must sit in the shift register which is the memory.

So, when a new frame arrives the encoder computes the codeword frame using the new frame and the stored previous m frame. And what do we mean by computes? It uses some kind of a logic circuit to do so. And once the computation is done the codeword frame is shifted out for transmission the oldest information frame in the memory is discarded because the new frame must be shifted in. And once this operation is complete we are now waiting for the next frame to come in and continue the process. Thus, for every k naught symbols that come in n naught symbols go out.

So, clearly the clock rates at the input and output are different please note convolutional encoders are very hardware fair friendly right. And since memory plays an integral part integral role in this, therefore the same k naught symbols are the input may, or may not generate the same n naught symbols at the output.

(Refer Slide Time: 09:00)

So, let us now define something called as a constraint length of a shift register encoder. So, the constraint length is defined as the number of symbols it can store in it is memory in terms of the input frames that is coming in right.

(Refer Slide Time: 09:20)

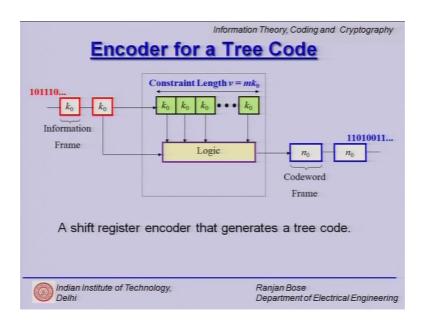

So, if you look at a general structure for a tree code it can be expressed as follows. So, let us start on the left hand side, we have the information frames coming in you have this long stream of input data say 101110 so and so forth. We first break it up into information frames of size k naught, my k naught can be as small as 1 it could be 2, 3 4, but whatever it is we break the input into k naught frames.

Now, if you see this dotted block is the encoder it has two components the memory which is the shift register and the logic is pretty much a set of x-or operations. Now if we look at the shift register here you will note that there are a certain number of information frames that can be stored in this shift register. And let us say nu equal to m times k naught, where k naught is the size of the information frame then the constraint length nu equal to m times k naught.

So, it tells me how many previous information frames have been stored in the memory? An intuitive understanding tells us that the larger the constraint length the stronger my code can be because I am not relying on more of the past information. Now once we have this going then the logic can be used to compute the codeword frame n naught, as you can see the codeword frame is longer than the information frame. If information frame is say 2 bit long then the codeword frame could be 3, 4, 5, if the information frame is 3 bits long, it could be 4 5 or 6.

(Refer Slide Time: 11:41)

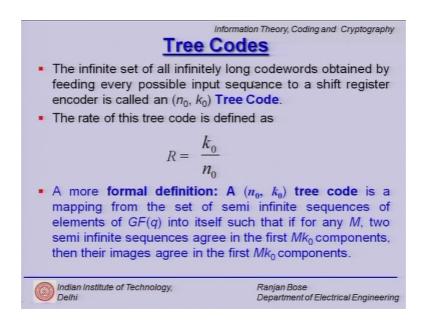

So, this structure generates for every k naught symbols or bits coming in n naught codeword frames. So, this infinitely long code words because input is infinite, so output is infinite it keeps going right it is called an n naught comma k naught tree code it is

distinguished from n comma k block code. So, we use n naught comma k naught where n naught is the output frame k naught is the information frame.

So, codeword frame n naught information frame k naught, and the code rate will clearly be k naught over n naught and you can have a more formal definition in terms of the image. So, a tree code is a mapping from a set of semi infinite sequences of the elements of GF q because we are not necessarily limiting us to binary into itself such that if for any M, two semi infinite sequences agree in the first M k naught component, then the image will also agree in the first M k naught components.

(Refer Slide Time: 12:45)

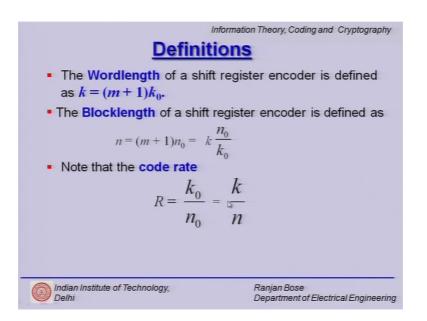

So, let us look at certain other definitions which will be useful to understand the tree codes first the word length. The word length can be defined in terms of this m remember m was used to define the constraint length. So, m plus one into k naught is k, which we defined as the word length and the block length n can be m plus 1 into n naught.

So, I can have a parallel understanding of the word length and the block length for the a tree code and code rate is nothing but k naught over n naught which can be easily expressed as your n and k the ratio of the word length to the block length.

#### (Refer Slide Time: 13:33)

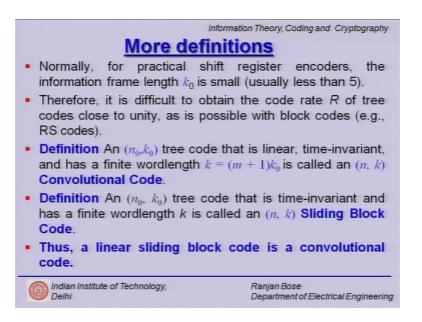

So, let us have some more definitions, so for practical shift register encoders to work the information stream length is typically small, there is a major difference from a linear block codes where k is huge. So, it could be 5 or less 7's are also common, but we would rather have small k naught.

So, code rate of this tree codes are not really close to unity because if k naught is for example, 5 then n naught can be 6, leading us to the best possible code rate of 5 over 6 we could have 5 over 7 5 over 8, but then we are looking it worse and worse. So, let us now understand what do we mean by a convolutional code which is actually used in real world application?

So, a n naught comma k naught tree code that is linear and time invariant and has a finite word length k given by this is called an n comma k convolutional code. So, we can easily see that the convolutional code is a subclass of a tree code, n naught comma k naught tree code that is time invariant and has a finite word length k is also called as a sliding block code. Therefore, a linear sliding block code is a convolutional code.

So, please note we are still in the dome domain of linear codes ok. So, linearity means the all 0 codeword would necessarily be a part of it and sum of two code words would also be a valid codeword in the definition of code words that we have just defined.

(Refer Slide Time: 15:24)

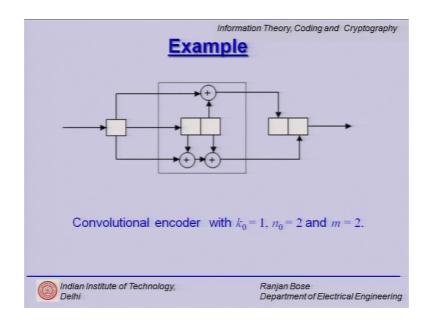

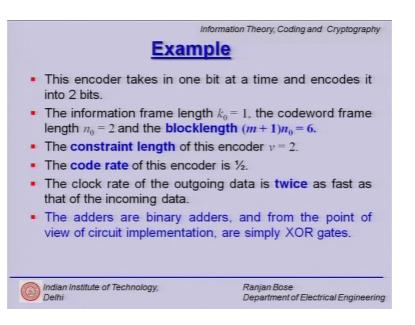

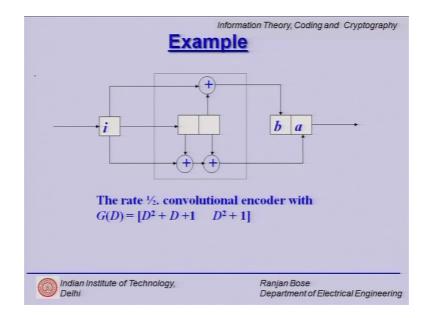

Now, let us understand this interesting concept using a simple example. So, here if you see on the left hand side your k naught is 1, you shift register has 2 bits and your output n naught has 2 bits. So, it is clearly a rate 1 by 2 encoder with k naught equal to 1, n naught is equal to 2, and m equal to 2 and the logic is as follows whatever is in this memory binary addition with the current input binary addition with the second stored bit gives you the output bit 2, an output bit 1 is nothing but the present incoming bit xored with the second stored bit will give you this output bit.

So, it is very quickly you one can calculate the output based on the input it goes as fast as the hardware circuit. And we know that a typical delay today in current circuit is less than a nanosecond, so we can have really fast encoders. (Refer Slide Time: 16:47)

So, this example takes one bit at a time and codes it into 2 bits leading at to a code rate of 1 by 2. The information frame length is k naught equal to 1, so for the block length is m plus 1 times n naught m is 2, 3, m plus 1 is 3 times n naught is 2 is 6. So, the effective block length is 6, constraint length of the same code rate is nu equal to 2, code rate half.

As we can say we have already observed and a clock rate of the outgoing data must be twice the input clock rate simply because for every one bit that is pumped into that encoder two bits must go out. So, the adders are all binary adders, so binary adders without carry which is simply the XOR gates ok, so very very hardware friendly implementation.

### (Refer Slide Time: 17:45)

| Information Theory, Coding and Cryptography<br>Example                                                                     |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| <ul> <li>Let us assume that the initial state of the shift register is [0 0].</li> </ul>                                   |  |  |  |  |  |  |  |

| <ul> <li>Now, either '0' will come or '1' will come as the incoming bit.</li> </ul>                                        |  |  |  |  |  |  |  |

| <ul> <li>Suppose '0' comes.</li> </ul>                                                                                     |  |  |  |  |  |  |  |

| <ul> <li>On performing the logic operations, we see that the computed value of<br/>the codeword frame is [0 0].</li> </ul> |  |  |  |  |  |  |  |

| <ul> <li>The 0 will be pushed into the memory (shift register) and the rightmost<br/>'0' will be dropped.</li> </ul>       |  |  |  |  |  |  |  |

| <ul> <li>The state of the shift register remains [0 0].</li> </ul>                                                         |  |  |  |  |  |  |  |

| <ul> <li>Next, let '1' arrive at the encoder.</li> </ul>                                                                   |  |  |  |  |  |  |  |

| <ul> <li>Again we perform the logic operations to compute the codeword frame.</li> </ul>                                   |  |  |  |  |  |  |  |

| This time we obtain [1 1].                                                                                                 |  |  |  |  |  |  |  |

| <ul> <li>So, this will be pushed out as the encoded frame.</li> </ul>                                                      |  |  |  |  |  |  |  |

| <ul> <li>The incoming '1' will be shifted into the memory, and the rightmost bit<br/>will be dropped.</li> </ul>           |  |  |  |  |  |  |  |

| <ul> <li>So the new state of the shift register will be [1 0].</li> </ul>                                                  |  |  |  |  |  |  |  |

| Indian Institute of Technology,         Ranjan Bose           Delhi         Department of Electrical Engineering           |  |  |  |  |  |  |  |

So, how does this encoder work in this example? So, basically we assume that the initial shift register at state is 00 that is the initial condition.

(Refer Slide Time: 18:00)

| Information Theory, Coding and Cryptography<br>Example                                                                                                                         |                                                     |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--|--|--|--|--|

|                                                                                                                                                                                | Drop the oldest bit                                 |  |  |  |  |  |

| Before                                                                                                                                                                         | After 🗟                                             |  |  |  |  |  |

| <ul> <li>Again, there are two possibilities regarding the incoming bit: '0' or '1'.</li> <li>It is possible to construct a table which lists all the possibilities.</li> </ul> |                                                     |  |  |  |  |  |

| Indian Institute of Technology,<br>Delhi                                                                                                                                       | Ranjan Bose<br>Department of Electrical Engineering |  |  |  |  |  |

Now input will be either a 1or a 0 and so what happens is if the initial condition is 00, for the shift register. We are only focusing on the shift register and the input rest all we have blanked out suppose the input is 1, then this 0 will go here, this 1 will go here, and the older 0 must be thrown out. So, after shifting in this portion 1 has shifted here, the 0 here

has shifted here, and the previous 0 has been thrown out discarded. So, we dropped the oldest bit and we can do.

(Refer Slide Time: 18:36)

| Information Theory, Coding and Cryptography<br>Example<br>The incoming and outgoing bits of the convolutional encoder |                 |                                 |                                                     |               |   |  |

|-----------------------------------------------------------------------------------------------------------------------|-----------------|---------------------------------|-----------------------------------------------------|---------------|---|--|

|                                                                                                                       | Incoming<br>Bit | Current State of<br>the encoder |                                                     | Outgoing Bits |   |  |

|                                                                                                                       | 0               | 0                               | 0                                                   | 0             | 0 |  |

|                                                                                                                       | 1 🗟             | 0                               | 0                                                   | 1             | 1 |  |

|                                                                                                                       | 0               | 0                               | 1                                                   | 1             | 1 |  |

|                                                                                                                       | 1               | 0                               | 1                                                   | 0             | 0 |  |

|                                                                                                                       | 0               | 1                               | 0                                                   | 0             | 1 |  |

|                                                                                                                       | 1               | 1                               | 0                                                   | 1             | 0 |  |

|                                                                                                                       | 0               | 1                               | 1                                                   | 1             | 0 |  |

|                                                                                                                       | 1               | 1                               | 1                                                   | 0             | 1 |  |

| Indian Institute of Technology,<br>Delhi                                                                              |                 |                                 | Ranjan Bose<br>Department of Electrical Engineering |               |   |  |

So, for all possible combinations of input bit, and the current state of the encoder, so, we did that example for 00, what if the 0 bit comes in 00. What if 1 bit input bit 1 comes in if the state of the encoder is 011011. So, clearly there are 8 possible combinations, so there are 8 entries into the table. And for each one of the input bit and the correct current state we have a calculation of the output bit based on the original state of the encoder which was as follows. So, whatever is the input bit and we have an output bit going.

# (Refer Slide Time: 19:30)

So, let us look at this example a little bit more carefully. So, we have an input block and then we have 2 bits as the encoder, and we have this going in here, binary adder here and this goes to your output. Similarly you have a binary adder here, the input bit comes in here and you have 1 here so n naught equal to 2 and k naught equal to 1.

Now if you were to look at the table you will realize that whatever is sitting here. If it was a 00 here, and a 1 comes in here, then this 1 shifts here and the older 0 shifts here, and the last one is discarded. And once you have that then these calculations can be conducted and you can do this basic calculation and it will give you the desired output right.

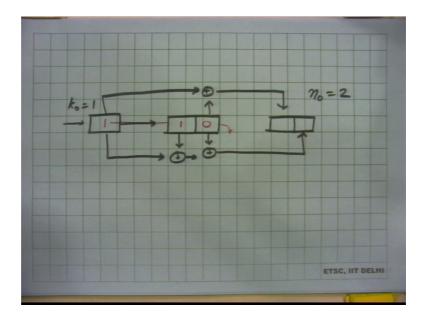

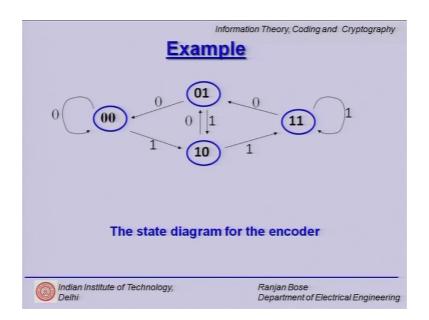

So, if we go back to our slides and we will see that it is possible to generate a table of in input bits, current state of the encoder and the output bits ok. Now suppose if you look at the next slide we can represent this as a simple state diagram. So, we can have the state diagram of the encoder in the slides, if you can see the state diagram you have a 00 as one of the states, 01 as one of the other states, 10 and 11.

# (Refer Slide Time: 21:25)

So, we have we have only 4 states, and we can see that depending upon whichever state you are sitting in if a 0 comes in your state does not change. But if a 1 comes in your state changes, if you are sitting in state 10 and if a 0 comes you become 01, but if a 1 comes you become 11 because the older bit will be thrown out this bit will be shifted here and a 1 bit will be shifted in the first place.

If you are sitting in 11, and a 1 comes you will retain your location as 11, but; however, if a 0 comes in the older bit will be thrown out the 0 will move in here, and the older 1 will move to this place leading it to a 01. Similarly if you are at 01, and a 1 comes then you will go to 10. So, you can make this a simple state diagram that you do for typical circuits.

(Refer Slide Time: 22:36)

So, we go to our slide where we show that we have the state diagram for the encoder this particular encoder. And these state diagram interconnections will change, if I change the logic circuit.

(Refer Slide Time: 22:50)

So, only 4 possible states are there and we have already represents the bits associated with each arrow in terms of the incoming bits. So, it can be seen that the same input bit gets encoded differently depending on the current state of the encoder, and in this way

this code with memory is different from the linear block code which gives the same output for the same input.

(Refer Slide Time: 23:19)

Now if you look at the state diagram the same information can be represented in a much more friendly manner, using a Trellis diagram. So, what is a trellis? A trellis is a graph whose nodes are arranged in a rectangular grid which is semi infinite to the right, and therefore, this code is also called as a trellis code. The number of nodes in each column is finite and is limited to the number of states.

(Refer Slide Time: 23:48)

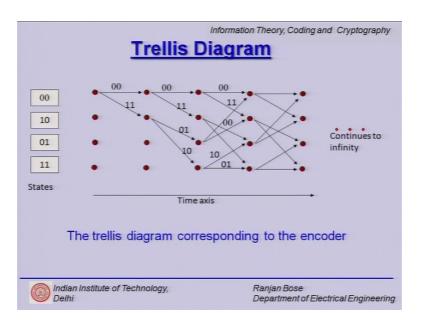

So, let us look at the same example the same state diagram now being recast as the trellis stack. On the left hand side we have the different states as you know there are only 4 states, 00, 10, 01, and 11.So, each of these nodes represent a state on the x axis we have the time axis that is each time an input symbol comes in a state transition may or may not happen, but we will move to the next level and the next level and the next level.

So, initially we are at state 00 represented by level 1, now if a 0 comes in you can see from your state diagram that you will retain your location in the state diagram as 00, so you continue to be the top node is the 00 state, but if a 1 appears as a input think a state transition will happen and you will move to 10.

So, there is an arrow connecting here, but please note regardless of whether a 0 comes in or a one comes in you can never go from state 00 to state 01 or from 00 to 11. So, certain state transitions are just not possible the transmitter knows this is the receiver knows this, but a noise does not know. So, this geometric structure together with the algebraic structure will add to the strength of our trellis codes ok, this is the point to be observed that we have now 2 r assistance a geometric structure as well.

Student: Sir.

Yes.

Student: So, but we can design the logic circuit instruction will get it may jump from 00 to 11.

So the question being asked is can we design our circuit diagram to have a transition from 00 to 11 sure you can, but please note then some other transition will not be possible. Because there will be only two branches emanating from every node every node is a state, one branch would correspond to input being 0, other should be corresponding to input being 1, there are only two possible inputs 0 or 1.

Student: But for a one we can for 0 it is going to (Refer Time: 26:17) with 00, but for the one incoming bit it may go to 01 or 11 that (Refer Time: 26:22).

Yes it can be possible that we can have a connection between this node and this node, but then there will be no connection between this node and this node. The point is no node is holier than the other node for me these are just 4 states, 4 nodes, whether it is moving from node 1 to node 2 versus node 1 to node 3. But it will not be able to transit from one node 1 to node 2 and 4.

So, some transitions are not legal that is the point of this exercise I know it receiver knows that noise does not. So, I will use this geometric structure also to help me reconstruct what was sent and it will be used the same trellis diagram will be used to decode the transmitted bit stream it is an important observation. So, if you continue with this trellis diagram notion then you will realize that for whatever state you are in there will be two emanating branches 1 for 0 input, and 1 for a 1 input.

On the top of each branches is the output of the encoder written. So, since it is n naught equal to 2, you will always find two bits written on every branch. So, this is a recast of the state diagram in terms of a trellis diagram, see it is semi infinite we know where it starts it does not end until infinity. So, it continues to infinity. Therefore, we call it semi infinite.

(Refer Slide Time: 28:08)

So, we have noted that every node is a state and then the rate is 1 by 2. So, 1 bit comes in and 2 bits go out, so, input bit can be a 1, or a 0 corresponding to two emanating branches from each node we can say that the top branch represents the input 0, and the bottom one represents a input as 1. And so output of the encoder is written on top.

#### (Refer Slide Time: 28:34)

So, this trellis diagram can be used to encode the input bit stream very very easily because we already have built in the time axis in there. It is not so using the state diagram where we have the same information, but not represented in along the time axis. So, encoding is very simple encoding is just following directions along the trellis diagram. So, we start with the top left node now if a 0 comes in follow the upper branch, 1 comes in follow the lower branch right.

So in fact, the input bit streams is 0111001 it is telling you go up up down down up up up down along the trellis. So, if you look at this trellis diagram, again if you have a 0, a 0 comes in we move here, 1 comes in we will go down, 1 comes in we move down, 0 comes in we go up up down down up and we just read out whatever is written on top of that branch that the transition along and that is the output. So, the input stream is just a direction that whenever you hit a node whether you go on top or you go on bottom.

So, it is extremely easy to encode it also shows a very important thing any particular bit stream to be encoded follows a path in the trellis which is a unique. So, input bit stream is corresponding to a unique path in the trellis there is no other way out. So, the decoding problem should be finding out the most likely path in the trellis and that is what we will pursue.

## (Refer Slide Time: 30:30)

So, let us say we have to encode this random bit stream 1001101 dot dot dot dot dot. So, we start with the top left and the moment we hit a 1, we take the lower branch 0, hit the upper branch hit the upper branch lower lower upper lower. So, it is up down up down and we can now look at the trellis diagram here.

(Refer Slide Time: 30:54)

So, since the input was 1001101 1 means down, 0 means well we have two options go up take the upper branch take the upper route. Another 0 means of these two branches which are emanating out please take the upper branch. Now I have reached here and I look at

the input reaches it says 1 take the lower branch, and it says 1 take the lower branch. Because please note along the x axis is the time axis as the input bit stream comes in I follow the paths.

So, I am sitting here and now I again look at 0, I take the upper branch I take get 1, I read the lower branch. And now I just read out what is written on top because the encoder for that state and input is already pre-calculated. So, I read out 11 01 11 11 10 10 00 and that is my nice looking output bit stream. For 7 bits of input we have 14 bits of output it is not a surprise because the rate is 1 by 2. So, clearly any particular input bit stream is a unique path in the trellis that I have shown here the red path is 10 01 011 input bit stream.

(Refer Slide Time: 32:30)

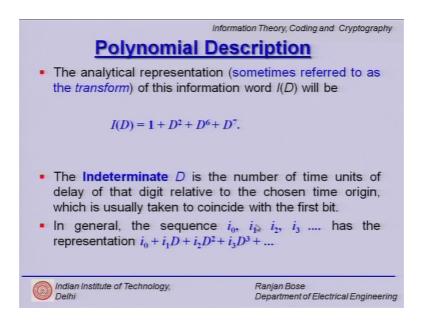

Now, we have a very nice succinct polynomial description. So, so far we have considered pictorial representation in terms of state diagram and trellis diagram we will now go for a polynomial description using a delay operator. Why a delay operator because it is very handy we have already a shift register where every shifting operation is a delay operation.

So, we already know that there is a one to one correspondence between a vector and a polynomial we have seen that in earlier convolutional codes. We will use the delay operator in a similar manner. So, we will have for example, this 10100011 with oldest

digit to the left and the most recent digit to the right as it enters the convolutional encoder.

(Refer Slide Time: 33:25)

So, the analytical expression will be also sometimes referred to as the transform in terms of I D is the following. So, it is nothing but 10100011 the coefficients of D, D cubed D raised power 4 except trellis all 0 they are corresponding to the 0's in the bit stream, the D is the indeterminate and is the delay unit. So, consequently any sequence i 0, i 1, i 2, i 3 can be represented as a i 0 plus i 1, D indeterminate plus i 2 D squared. So, it tells you where in the location in terms of time frame my bits are.

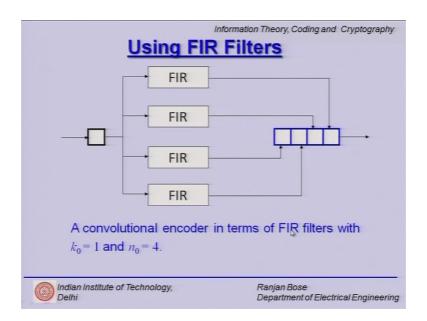

(Refer Slide Time: 34:13)

So, we can have very efficient FIR based representation. What do you have is an input bit stream and of which k naught is the symbol frame input frame we have FIR here and then linked to the output. These FIR's are nothing but memory and logic.

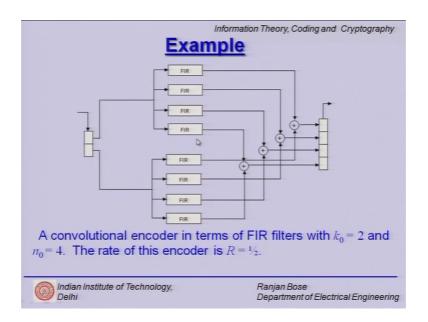

(Refer Slide Time: 34:35)

Similarly, I can have a more complex setup here in in example k naught is 2, as you can see n naught is 4. So, the rate is 1 by 2 and you can have additional FIR filters, so this is to illustrate that it is extremely hardware friendly this is a salt problem we can build very efficient encoders for convolutional codes.

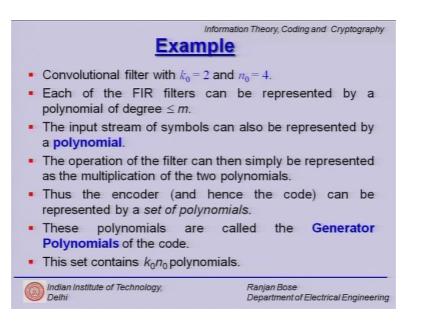

#### (Refer Slide Time: 35:00)

So, we just now saw an example of k naught is equal to 2, and n naught is equal to 4, but can we represent this encoder using a polynomial matrix or generator polynomial matrix. Well, the answer is yes all we have to do is learn how to do an input output relationship.

(Refer Slide Time: 35:23)

| Information Theory, Coding and Cryptography                                                                                                         |                                                     |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--|--|--|--|--|

| Generator Polynomial Matrix                                                                                                                         |                                                     |  |  |  |  |  |

|                                                                                                                                                     |                                                     |  |  |  |  |  |

| <ul> <li>The largest degree of a progenerator polynomials is m.</li> </ul>                                                                          | olynomial in this set of                            |  |  |  |  |  |

| <ul> <li>Recall that a block code was represented by a single<br/>generator polynomial.</li> </ul>                                                  |                                                     |  |  |  |  |  |

| <ul> <li>Thus we can define a Generator Polynomial Matrix of<br/>size k<sub>0</sub> × n<sub>0</sub> for a convolutional code as follows.</li> </ul> |                                                     |  |  |  |  |  |

| $G(D) = [g_{ij}(D)].$                                                                                                                               |                                                     |  |  |  |  |  |

|                                                                                                                                                     |                                                     |  |  |  |  |  |

| Indian Institute of Technology,<br>Delhi                                                                                                            | Ranjan Bose<br>Department of Electrical Engineering |  |  |  |  |  |

So, the largest degree of a polynomial which in the set of generator polynomial is m, and a block code if you recall was used represented using a single generator polynomial, but here we will have a generator polynomial matrix linking the input to the output ok. So, finally, we have to link say k naught input bits to n naught output bits through a delay register. So, let us look at a very simple example it is our previous example.

(Refer Slide Time: 36:00)

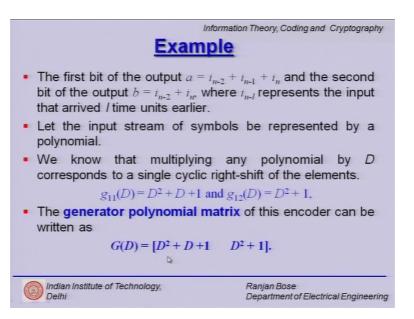

So, k naught is 1, n naught is 2, and then 2 elements in the shift register. But if you look at the output in this first bit well it takes the current bit the previous bit and previous to that bit. So, current no delay D raise power 0, 1 delay D raise power 1, 2 delays D raise power 2.

So, this first one is linked to the input as D square plus D plus 1, but if you look at b the second output we should be the second element of the matrix it is nothing but the input D raise power 0 plus not the first delay, but the previous to previous that. So, D squared, so D squared plus 1, so all I am doing is relating the input to the output through the series of delays right.

(Refer Slide Time: 37:00)

So, this is the example how we input and output are relate a and b are related using the D square. So, we have these two elements of the generator polynomial matrix g 11 and g 12 linking input one to output one input one to output two. And so we have consequently the notion of a generator polynomial matrix which we will now write as D squared plus D plus 1 and D squared plus 1.

So, the same the entire hardware encoder can be represented using this generator polynomial matrix. So, if you give me the encoder in hardware I will give you the generator polynomial matrix, if you give me the generator polynomial matrix I will give you the hardware implementation of the encoder ok.

(Refer Slide Time: 38:00)

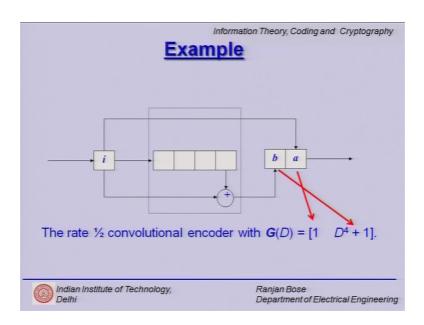

So, let us look at another simple example again we have 4 memory elements, well I first look at a, a this a is nothing but the input nothing else. So, it gives me a feeling that it should be just 1, and it is going to be a systematic convolutional encoder because the first bit goes right like that.

The second is their parity and how are we calculating the parity well it is the same bit and XORed with 4 bits that came before in the bit stream. So, it is delay D 4 plus 1 ok, so this is the generator polynomial matrix for this, so a is 1, and b is D 4 plus 1.

Information Theory, Coding and Cryptography

Example

Generator polynomial matrix of this encoder can be written as

G(D) = [1 D<sup>4</sup> + 1].

Note that the first k<sub>0</sub> bits (k<sub>0</sub> = 1) of the codeword frame is identical to the information frame.

Hence, this is a Systematic Convolutional Encoder.

(Refer Slide Time: 38:49)

So, we have the generator polynomial matrix representation as follows and we can say that this is clearly a systematic convolution encoder.

(Refer Slide Time: 39:00)

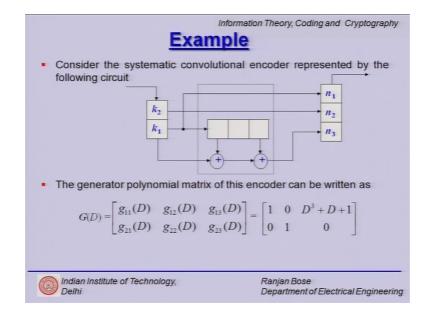

So, if you look at this example again we have now input k 1 and k 2, output n 1, n 2 and n 3 again we have 3 bits and we have clearly a logic units. Please note in this example we have interestingly put k 1 just going into this 1 ok. So, the constraint length will be defined with respect to only k 1, please note this 3 units in the memory is not a multiple of this k 1, k 2 and k naught equal to 2. So, now, we have 3 outputs related to 2 inputs, so there should be 6 elements in this, so it is a 2 cross 3 generator polynomial matrix.

Now, if you look at it n 1 is nothing but k 1, so it is just a 1 n 2 is directly linked to k 2 looks like we are again n for a systematic convolutional encoder. So, this is this g 22 is 1 node, n 1 is no way linked to k 2, so it is 0, n 2 is no way linked to k 1 it does no connection. So, it is a 0, so you have a small identity matrix right here and here the fun begins n 3 is related to k 1. So, g 13 is now 1 plus a delay plus D cubed this is D D square D cube. So, n 3 is D cube plus D plus 1, but n 3 in no way is related to k 2, so there is a 0. So, just by a visual inspection I can write the generator polynomial matrix.

So, we will use visual inspection.

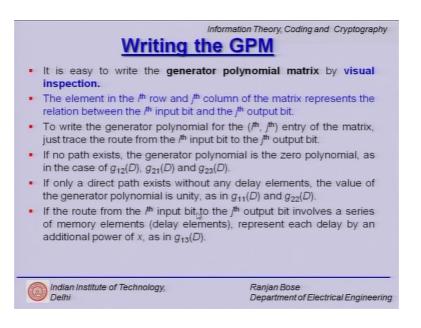

## (Refer Slide Time: 41:00)

And immediately write the generator polynomial matrix there just trying to write the elements of i-th row and j-th column using the input output relationship. So, if no path exists then it is 0, as we see saw for g 12, g 21, and g 23 there is absolutely no connection between say k 2 and n 3.

And if there is a direct path then it is unity as we saw in g 11, and g 22 and thereby we got the identity matrix. And just all is you have to just observe how many delays you are going through.

(Refer Slide Time: 41:40)

So, with that we come to the end of this lecture let us summarize what we have learnt so far. We started off with the definition of tree codes and convolutional codes, and then we found a very very interesting pictographic representation of trellis codes using trellis diagrams.

We learnt how to use this trellis diagram to encode very efficiently an input bit stream we also made a very very interesting observation that any particular input bit stream corresponds to a unique path in the trellis. We then went on to define what do we mean by polynomial description of convolutional codes. And finally, we were able to represent any encoder in a hardware using a generator polynomial matrix.

With that we come to the end of this current lecture.