## Foundation to Computer Systems Design

# **Indian Institute of Technology Madras**

## Professor V. Kamakoti

## **Depratment of Computer science and Engineering**

### **Module 1.3 Basic Gates**

(Refer Slide Time: 00:21)

| [6 (2 Yee joet β 500 104 (9)<br>இதிய Ω P 4 3 0 7 € " Z = Z + 2 + 9 " 3 5 €<br>Β / ■ ■ ■ ■ ■ ■ ■ ■ ■ ■ ■ ■ ■ ■ ■ ■ ■ ■ |                         |            | (*)   |

|-----------------------------------------------------------------------------------------------------------------------|-------------------------|------------|-------|

|                                                                                                                       |                         | Module 1.3 | NPTEL |

|                                                                                                                       |                         |            |       |

|                                                                                                                       |                         |            |       |

|                                                                                                                       |                         |            |       |

|                                                                                                                       |                         |            | -     |

|                                                                                                                       | Module 1.3; Basic Gates |            |       |

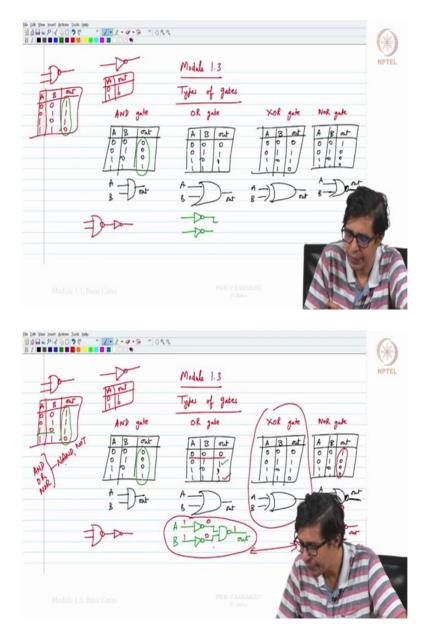

Module 1.3 first our third module in this module we will see different types of gates we have already seen that NOT gate and the NAND gate now we will see a set of gate one is called AND gate another is the OR gate, you will also see XOR gate and NOR gate. These are basically we will, we will represent every gate by its what we call as the truth table all of them are binary gates to starts with so we will be draw we will be describing that behaviour using the truth table so A and B are input and Out is the output for each of this gates.

So zero zero, zero one, one zero, one one so the AND gate is like this OR gate is like this, XOR gate is, and NOR gate sorry OR gate is zero one one one. Okay so these are all the four basic gates we have already seen two more gates in the previous module namely the NAND gate and the not gate so the and gate is represented like this the OR gate is represented like this the XOR gate like this the NOR gate is represented like this the NOR is nothing but OR gate representation followed by a small circle in front.

Now how are these gates related now let us just quickly reuse it back how NAND gate was defined, NAND gate was defined by and the NOT gate which are a single input and output was defined as zero one, one zero, you can easily check there and function is nothing but the NAND function followed by a NOT gate. So already verify this very quickly you can see if you take the output one one one one zero for a given inputs and you inward them.

So this one one zero will become zero zero zero one and that is exactly the output of the and gate correct and similarly right so the NAND gate basically can be expressed like this now you can also see that the OR gate is nothing but.

(Refer Slide Time: 4:58)

So both these functionality are same for example that OR gate is this how do you get this the OR gate is nothing but if you let us just check one or two let us say zero zero this will be one one and one one of NAND is what zero. So zero zero I give zero similar let us say zero one this will be one ane this will be zero one of zero NAND one of zero, one zero NAND as you see here one zero NAND is one. So I get this one similarly I can check for one zero it will be the same now let us check for one one I give zero zero.

And this is one so, so I get one right so that NOR gate can again be represented as the NAND gate or not gate. Now what is the OR gate can be represented as a combination of not gate and NAND gate and gate can be represented as a combination of NAND gate and not gate. Now NOR gate is nothing but OR gate followed by NOT both are same right so if you take zero one one this is the OR gate output.

And when you inward it give it to the inverter as you see here this one this zero one one one will become one zero zero zero for the NOR gate as you see here so and since OR gate can be represented as a combination of not and NAND the NOR gate itself can be now represented as a combination of NOT and NAND right so if you just replace this OR gate with this right you get basically not a NAND representation of nor gate.

So what we have seen here is even and the gate your OR gate and NOR gate all of them can be represented using NAND gate comma NOT gate right. We will talk about the XOR gate slightly later but XOR gate is the same as OR gate excepted one one will be zero rather than one one will be. In the case OR gate one one is one while gate of XOR gate one one is zero. Right right now we will see something once it so what if slowly coming out is all these basic gate is namely OR and NOR can be represented using Using AND NOT now let us take this.

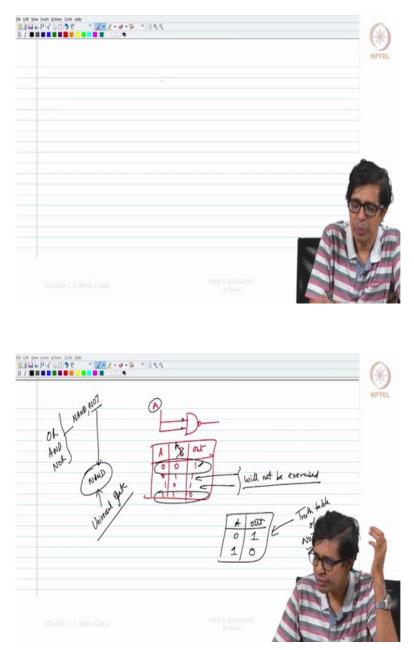

# (Refer Slide Time: 8:44)

Now let us see suppose I connect to both the input of a NAND gate the same A what will be the output so we know that A B is out zero zero is one, zero one is one, one zero is one, one one is zero this is what the NAND gate this is how the NAND gate behaves this is the true table of the NAND gate now if I connect both the inputs to the same line that means only two of this four inputs are exercised this.

And this because since both the inputs are connected to the same line A the second and the third will not be exercised. So so essentially this B also becomes A so now when you see this

table when I apply A the out when I apply zero to A what I get is one and when I apply one to A I get zero now what is this, this is nothing but a truth table of NOT gate.

So now you will see OR AND and NOR can be represented using NAND, NOT now NOT itself can be represented as NAND so NAND can represent all the four other gates namely OR, NOT and then NOR right so NAND is we call it as an universal gate. So NAND we call it as a universal gate.

Right thats why this course is also called NAND to tetris universal gate means anything can be build using the NAND gate right now we will come to the last part of this particular module.

(Refer Slide Time: 11:14)

Which is the XOR gate, XOR gate is built like this as you have seen in earlier zero zero is zero, zero one is one, one zero is one, one one is zero. So we can basically built this as these all are NAND gates so let this be AB right so this is AB and this is XOR function so suppose I apply zero zero here by the NAND gate this becomes one this becomes one cause this is zero, zero one is one for this NAND gate zero one is one one is zero.

So when I apply zero zero I get zero. Then I apply zero one, zero one this is one, one one this becomes zero, zero one this is one this is correct one zero becomes one. So zero one is one, similarly one zero can be shown as one suppose I put one one this becomes zero since this is zero this is one and this is also one both of them are one and one one again become zero. So the XOR gate that we described can also be built using NAND gates right.

So so the NAND gate can now built what are the gates it can built and XOR gate using NAND gate I can built an XOR gate I can built AND gate, OR gate, NOR gate and the NOT gate itself ((())(13:30) so every gate that we have seen so far can be basically built using NAND gate and thats why NAND gate is called an universal gate.

And we will and this course basically tries to use an NANDgate to built several the entire computer on which you are going to execute that tetris game so thats how the name NAND to tetris has come.